ルネサス テクノロジ、日立製作所、早稲田大学および東京工業大学の研究チームは、複数のCPUコアと特定用途向けプロセッサを搭載したヘテロジニアスマルチコア型システムLSIを開発、電力性能比37GOPS/Wを実現したことを発表した。同成果の詳細は、米国にて2月7日より開催されている半導体の国際学会「ISSCC(The International Solid-State Circuits Conference)」において、2月8日(現地時間)に発表される予定。

今回開発したヘテロジニアスマルチコアLSIは、コアとして汎用の32ビットRISCマイコン「SuperH」のCPUコアである「SH-4A」を8個、動的再構成可能プロセッサのコア「Flexible Engine(FE)」を4個、マトリックス型超並列プロセッサの「MX-2」コアを2個搭載しているほか、VPU(Video Processing Unit)を1個、SPU(Sound Processing Unit)を1個集積しており、各コアに特性に応じて処理を割り振ることで、処理効率を高めることが可能となる。

例えば、例えば顔画像を検出する映像処理に適用した場合、顔の検出を"MX-2"に、その動きの検出を"FE"に、顔データのデータベース検索を"SH-4A"に割り当てることで、高性能な処理を高速に実現することができるようになる。

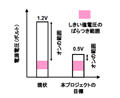

試作チップのクロック周波数は最大で648MHz、処理性能は最大114.7GOPS。消費電力は648MHz動作時で約3.07Wであり、単位電力当たりの性能は37GOPS/Wとなる。

また、従来のSH-4Aはすべて16ビット幅命令でシンプルかつ高効率である反面、命令種別の制約によりコンパイラによる動作最適化を十分に行うことができない場合があった。今回試作チップに搭載したSH-4Aには、約130個の32ビット幅の新規命令を追加。これにより、従来のSH-4Aにおける制約を補完することが可能となり、命令コードの最適化で、SH-4Aの面積増加を2%以下に抑えながら、Dhrystone2.1で16%の性能向上を果たすなど、全般的に従来比10~34%の性能向上が可能となった。

さらに、20を超すプロセッサ、コンポーネントを搭載していることから、単一アプリケーションで使用するメモリ領域が不足する可能性があるため、物理アドレス空間を32ビットから40ビットに拡張している。これにより、物理アドレス空間は1TBまで扱うことが可能となった。また、これに合わせてSH-4Aの拡張と特定用途プロセッサ間でのデータ通信を行うためのデータ転送ユニットの拡張も実施。これにより、SH-4AのCPU性能を消費することなくSH-4Aと特定用途プロセッサ間でのデータ通信を行うことが可能となった。

このほか、早稲田大学 笠原博徳・木村啓二研究室が開発したヘテロジニアスマルチコア用自動並列化コンパイラを用いることで、汎用用途CPUコアと特定用途プロセッサコアへの自動的な処理の割り当て、自動消費電力低減制御を可能とした。具体的には、同コンパイラを用いると、早稲田大学内に設置したヘテロジニアスマルチコアアーキテクチャ・API検討委員会にてIT・半導体企業6社ともに開発したOSCAR APIヘテロジニアスマルチコア拡張を用いて、逐次プログラムからヘテロジニアスマルチコア用の並列プログラムの自動生成、各コアごとの周波数・電圧制御・クロックゲーティングによる消費電力低減制御を行なうことができる。

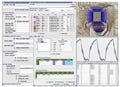

また、東京工業大学 前島研究室が開発したヘテロジニアスマルチコアに向けたソフトウェア統合開発環境を用いることで、各種アプリケーション・プログラム開発におけるデバッグ時間の短縮などが可能となり、結果として、ヘテロジニアスマルチコアLSI用ソフトウェア開発期間の短縮の実現が期待されるという。