Nehalemのコアのサイズは32平方mm程度であり、同じ45nmプロセスで製造されるPenrynのコアが21~22平方mmであるのに較べると1.5倍程度に大きくなっている。チップ写真からは、1次、2次のキャッシュが大きな面積を占めているというわけでは無く、ロジックで面積が増加しているようである。しかし、公表された機能強化だけでは、これほどの面積増加が必要とは考えられないので、隠し機能が搭載されている可能性もある。

|

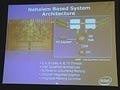

ClovertownとHarpertown(出典:Intel) |

このClovertownとHarpertownのスライドは、完全に正しいのであるが、誤解を招き易い。Harpertownについて言うと、45nmプロセスで作った2コアのPenrynが2チップで構成されているという絵であり、それぞれのチップが107平方mmと書かれている。そして、820Mトランジスタと12MBキャッシュは2個のチップの下に書かれており、これは2チップ合計の値である。つまり、107平方mmのPenrynは、410Mトランジスタでキャッシュは6MBである。

上の図のように、Penrynの6MBのキャッシュはおおよそ40平方mm程度の面積を占めている。一方、チップ写真から判定すると、Nehalemのキャッシュは90平方mm弱を占めており、この面積から推定すると12MBのキャッシュを搭載していると考えられる。しかし、Nehalemのトランジスタ数は731Mと発表されており、これはHarpertownの820Mトランジスタよりも少なく、12MBのキャッシュと4コアのトランジスタ数としてはちょっと少ない数である。噂で言われているようにキャッシュは8MBで、それに加えて、今回は、合計トランジスタ数に含めていない将来の拡張用の隠しキャッシュが搭載されているのかも知れない。