ポストムーア時代のアーキテクチャ設計メソドロジ

LBNLのGeorge Mikelogiannakis氏はポストムーア時代の設計メソドロジについて述べた。

ポストムーア時代には、新しいトランジスタ、新しいメモリ、3Dチップ積層、新奇なアーキテクチャと多数の選択肢がある。どのようにして選択を行うのかが大きな問題であるという。

-

新しいトランジスタ、新しいメモリ、3Dチップ積層、新奇なアーキテクチャと多数の選択肢がある。どのようにして選択を行うのかが問題 (ここからの図は、LBNLのGeorge Mikelogiannakis氏の発表スライドを撮影したものである)

さらに、新奇なデバイスやテクノロジは、小規模なシステムでは確認されていても、本格的な大規模なシステムで使えるかどうかは確認されていないことが多い。また、デバイスの量産が可能か、セルライブラリが使用可能か、ポピュラーなCADで使えるか、などなど不明な点が多い。

また、アーキテクチャ設計では、ホモジニアスなマルチCPU構成だけでなく、ヘテロジニアスな各種モジュールをネットワークでつないだり、アクセラレータを接続したり、メモリも不揮発性メモリを使ったり、3D積層の高バンド幅メモリを使うなど、多くのバリエーションが考えられるが、これらのアーキテクチャをどのようにして評価すればよいのであろうか。

-

ホモジニアスから各種のへテロジニアスなアーキテクチャ、アクセラレータの使用、不揮発性や3D積層の高バンド幅メモリを使うかなど、アーキテクチャ的にも多くの選択肢がある。これらのバリエーションをどのように評価すべきか

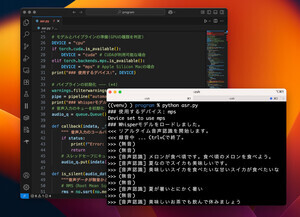

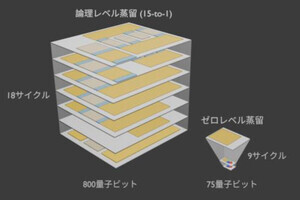

次の図の左端の列のツールは入力に対してTFET(トンネルFET)やCNFET(カーボンナノチューブFET)などの素子のモデルを作り、デバイスレベルのシミュレータでトランジスタの電流、電圧特性を計算する。左から2番目の列は、素子の電圧、電流特性を入力としてインバータやアダーを作り、デバイスレベルのシミュレータで遅延時間や電力を計算する。

3列目のツールは、特定のアーキテクチャの論理レベルの記述をRTLシミュレータなどでシミュレートし、遅延時間や消費電力を計算し、4列目のツールは、チップマルチプロセサなどのアーキテクチャをシミュレートして遅延時間や消費電力を計算する。

このようなツールチェインで、新しい素子を使った各種のアーキテクチャのシステムの性能や消費電力を計算することができる。

アーキテクチャ設計のメソドロジとしては、アプリケーションからその動きを抽出する評価を行い、アーキテクチャ上の選択肢を入力としてシミュレーションを行い、良さそうな候補を選択する。そして、これらの候補をさらにチューニングして改良を加えたものを出力する。このようにすれば、将来のデバイスを使うアーキテクチャの設計とその評価が可能である。

広範な選択肢の中から最適なアーキテクチャ設計を選択するスキームとしては妥当な考え方であると思うが、各種の新奇なデバイスを設計するのは大変であり、信頼できるデバイスシミュレータを作るのも大変である。大きく異なる選択肢の優劣を比較する場合、遅延時間や消費電力の計算精度が実用に耐えるかなど、いろいろと問題はありそうである。

HPCワークロードの変化とエクサスケールの先はどうするのか

DoEのBill Harrod氏は、システムの観点から、今後、ワークロードがどのように変わっていくのか、エクサスケールの先はどうするのかについての考察を述べた。

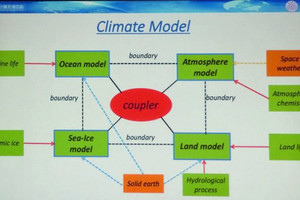

従来のHPCがビジネス分野や政府のモデリングやシミュレーションに使われるようになってきている。このため、扱う問題の規模が大きくなり、より高いモデル精度が必要になってきている。また、金融やパーソナライズした医薬品の開発、サイバーセキュリティなどの分野でもビッグデータ解析などが使われ始めている。

さらに、AIやディープラーニングもサポートできる新しいHPCシステムが要求されてきている。

-

HPCのワークロードが変わってきている。既存のHPCがビジネスや政府部門で使われ、規模の拡大やモデル精度の改善が要求されてきている。また、金融やパーソナライズ医薬品の開発など、ビッグデータを扱う新たなHPCが出てきている。また、AIやディープラーニングのサポートも要求されてきている

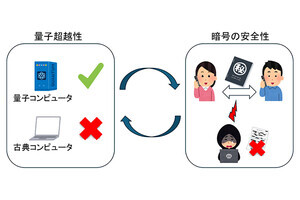

そして、将来のハードウェアテクノロジを見るといくつもの大きなチャレンジがある。ITRSでは、2028年に現在のムーアの法則は止まってしまうと予想されている。一方、アーキテクチャでは量子コンピューティング、ニューロコンピューティングなどいろいろなアーキテクチャが提案されているが、どれが良いのか議論は収束しそうにない。

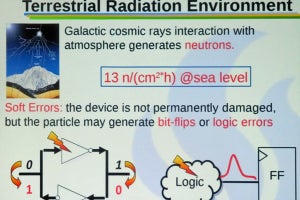

また、計算パラダイムもローカルにデータを置く計算法、新しいアルゴリズムなどが出てきている。そして、ECCなどよりももっと高いレイヤでのエラー訂正も必要になる。

-

CMOSの改良は頭打ちである。量子コンピューティングやニューロコンピューティングなどいろいろなアーキテクチャが提案されているが、どれが良いかは判断しがたい。用途の広がりで、新たな計算パラダイムが必要となっている

エクサスケールのシステムはなんとか作れそうであるが、その先はどうなるのか? ゼタスケールを目指すのか? しかし、単に演算性能が上がるだけではあまり興味を持たれそうにない。

Harrod氏は、コンピューティングの将来の不確実性から、テクノロジの転換点を迎える。テクノロジによって性能を向上させるという挑戦が必要になると言う。

エクサスケールの先のスパコンの特性はどうなるのか? どのようなワークロードが設計の方向性を決めるのか?

必要に応じて専用システムを作るのか、汎用システムを作るのか? どのようなテクノロジが性能向上を可能にするのか? システムは効率的で生産性の高いものである必要があり、かつ、より大規模の問題が解ける必要があるが、どのようなものを作ればよいのか?

これを2028年-2030年ころに作るのか、それとも、もっと小刻みに性能を上げていくべきか?

エクサスケールの先については、National Strategic Computing Initiativeを推進するディレクタであるHarrod氏は疑問を列挙しただけである。要するに、学会や業界でもエクサスケールの先をどうすべきかについて一貫性のあるストーリーが出来てくるまでには、まだまだ、時間が必要な状況であると思われる。