Cray Y-MP

1982年にX-MPが発売され、Cray Researchのビジネスはつながったのであるが、Cray-2は、まだ、開発が続いており、その完成を待っていればよいという状況ではなかった。このため、Cray ResearchはCray X-MPの改良版を作る必要があった。これが「Cray Y-MP」である。

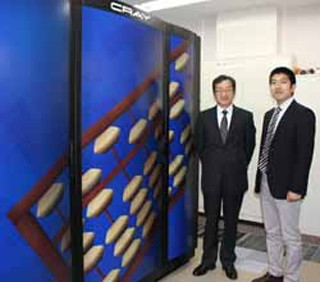

Y-MPはX-MPと同様の実装でCの字型のキャビネットを使い、それに直線のキャビネットが加えられたので、平面図で見るとディズニーの有名キャラクターのような耳がついたY字型になった。これもY-MPという命名に関係しているのかも知れない。しかし、途中から、図1.56のような角形のキャビネットが使われるようになり、Y字型のキャビネットは使われなくなってしまった。

Y-MPの開発は、X-MPを開発したSteve Chenに任されたが、Steve Chenは野心的な新技術や新機構を盛り込んで、Y-MPの性能を高めようというアプローチをとった。その結果、Y-MPの開発は多額の開発費を食い、また、遅れが目立つようになってきた。これでは保険が保険にならず、Cray Researchに2つの野心的プロジェクトは必要ない。

このため、Cray ResearchはSteve Chenを解任し、Y-MPの開発はLes Davisが担当することにした。

Les Davisは、プロジェクトをより堅実なCray X-MPの改良という方向に引き戻した。Cray Y-MPでの主要な改良は、アドレスを24bitから32bitに拡張したことと8プロセサ構成が追加されたことである。

8個のプロセサは図1.57に示すように、4×4と8×8のクロスバで256バンクのメモリと接続されていた。

また、Y-MPでは2500ゲートのECLカスタムLSIを使い、クロックを167MHz(6ns)まで引き上げた。これで各プロセサのピーク性能は333MFlopsとなり、8プロセサ化とあいまって、ピーク演算性能は2.67GFlopsまで向上した。また、ECLのメインメモリを64MWまで搭載可能にした。このCray Y-MP Model Dは、1988年にリリースされた。この3年前にCray-2がリリースされているが、市場ではY-MPの方が売れたようである。

Cray Y-MP Model Dの最大メモリ量を4倍の256MWに拡大し、IOサブシステムのバンド幅を2倍に引き上げたモデルが1990年にリリースされた。このモデルはCray Y-MP Model Eと呼ばれる。

さらに、1992年には、DRAMを使ってメインメモリを4GWに拡大したCray Y-MP M90シリーズがリリースされた。DRAMであるので、メモリアクセスは遅いが、大量のメモリを必要とする処理には威力を発揮する。

(次回は11月9日の掲載予定です)