その結果、実際にALD法を用いてIn2O3を三次元構造に均一に成膜できることが確認され、作製された薄膜トランジスタの移動度が40cm2/Vsを超えることも確認されたとする。

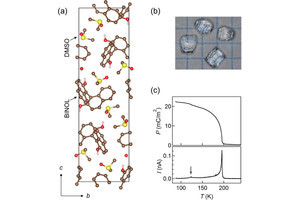

また、ALD法を用いて、二酸化ハフニウムジルコニウム(HfZrO2)強誘電体をゲート絶縁膜とするFeFETを試作したところ、理論的に予測された通り、1.5V程度のメモリウィンドウ(しきい値電圧差)、1万回を超える書換耐性、1000秒を超える保持特性が実証されたとする。

-

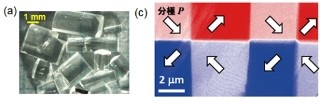

(a)提案されている酸化物半導体をチャネルとした三次元垂直チャネル型FeFETの模式図。ゲート絶縁膜には強誘電体HfO2が用いられている。(b)酸化物半導体を三次元構造に成膜するときの問題と解決法。ALD法を用いることで、三次元構造に均一に成膜できる (出所:プレスリリースPDF)

さらに研究チームでは、反強誘電体の二酸化ジルコニウム(ZrO2)をゲート絶縁膜とする、「反強誘電体トランジスタ」(AFeFET)の提案も行っている。酸化物半導体はN型半導体であり、多数キャリアである電子を誘起しやすい一方、少数キャリアである正孔を誘起しづらいことにより、プログラム状態に対して消去状態の保持特性が劣化しやすい特徴があることから、反強誘電体を用いることで、少数キャリアを誘起しなくても効率的に消去動作が可能となり、消去状態の保持特性を改善できるとする。

-

(a)試作された三次元垂直チャネル型FeFETの断面透過型電子顕微鏡画像。強誘電体HfO2と酸化物半導体であるIn2O3が共に均一に成膜されている。(b)試作したプロトタイプデバイス全体の断面模式図 (出所:プレスリリースPDF)

研究では、0.7V程度のメモリウィンドウ、1万回を超える書換耐性、1000秒を超える保持特性が実証されたとのことで、この技術は高密度かつ低消費電力であるため、IoTデバイスのストレージメモリに用いることで、ビッグデータを利活用する社会サービスの展開が期待されるとしている。

なお、今後については、多元素系酸化物半導体をALD法で成膜する技術の研究開発を継続して進めていき、高移動度かつ高信頼性のある酸化物半導体の三次元構造への均一な成膜を目指すとしているほか、三次元積層数を増やして集積数を上げて高密度化を目指すともしている。また、実用的な書換速度の実証に向けて、ゲート、ソース、ドレインでの寄生抵抗を減らした設計とプロセスインテグレーションも進めていくとしている。