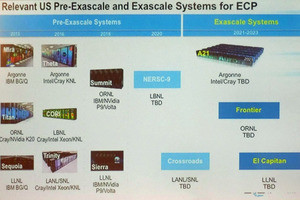

AMDは米国時間の11月8日、「AMD Accelerated Data Center Premier」と題したオンラインイベントを開催し、ORNL(米オークリッジ国立研究所)の1.5EFlopsを発揮する次世代スーパーコンピュータシステムである「Frontier」に採用を予定しているカスタム版EPYCと「Radeon Instinct MI200」の詳細を公開した。この内容を、事前説明をベースにご紹介したい。

もともとORNLのFrontierは、2021年中に設置が終わり、2022年から稼働予定となっている。AMDがこの時期に説明を行うというのは、すでにFrontier向けのシステム設置完了がほぼ確実になった(というか、順調に設置が進んでおり、年内に稼働開始が確実になった)事を意味していると考えて良いかと思う。さてそのFrontier、すでにORNLのFrontierのページからスペックシートやノード構成図(Photo01)が公開されているが、個々のコンポーネントについては、

- CPU:HPC and AI Optimized AMD EPYC CPU

- GPU:Purpose Build AMD Radeon Instinct GPU

とあるだけでその詳細は明らかにされていなかった。

-

Photo01:概略図。1つのBlade Serverに2つ分のノードが収まる格好になっている。ノード間接続はSlingshotであるが、SlingshotのI/FはEPYCではなくRadeon Instinctにつながっているあたりがちょっと面白い

3D V-Cacheを搭載したカスタム版EPYC

さて、まずEPYCについて。こちらは予想通りであるが、3D V-Cacheを搭載したEPYCを投入することが明らかにされた(Photo02,03)。

ここで総容量804MBというキャッシュであるが、要するに1つのEPYCに8つのダイが搭載されるが、このダイあたり

- L1:(Inst 32KB+Data 32KB)×8=64KB×8=0.5MB

- L2:Unified 512KB×8=4MB

- L3:Unified 32MB+64MB V-Cache=96MB

となり、合計100.5MB。EPYCはこれを最大8ダイ搭載するので、100.5×8=804MBとなる計算だ。

このV-Cache搭載EPYC、Photo02にもある様に50%程度の性能改善が期待できるとしており、実際16コアのEPYC同士で比較した場合に66%の性能改善が見られたとしている(Photo03)。

すでに多くのパートナーがこの3D V-Cache搭載EPYCに対応を行っており(Photo04)、2022年第1四半期には一般顧客向けにも提供を開始するという話であった(Photo05)。

-

Photo04:これはSynopsysのVCSという半導体デザインの検証ツールを実施した場合の結果

-

Photo06:もちろん、これに先んじてORNLには納入が進んでいると説明されており、要するに量産はとっくに開始。特定顧客向けにはすでに提供開始しており、一般顧客向けの提供が2022年になる、という話である

CDNA2アーキテクチャ搭載のRadeon Instinct MI200シリーズ

次がRadeon Instinctであるが、こちらは現在のRadeon Instinct MI100の延長ではなく、CDNA2アーキテクチャを搭載したRadeon Instinct MI200シリーズをFrontierに納入する事を発表した(Photo07)。

-

Photo07:ここで言うcompetitorはNVIDIAのA100の事だが、今後はこれにIntelのPonte Vecchioが加わることになる。というか、Frontier vs Auroraという図式で考えると、むしろcompetitorはPonte Vecchioが本命ではなかろうか?

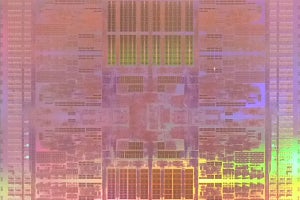

さて、こちらもなかなかお化けである。構成そのものは2ダイで、それぞれが586億トランジスタ、XCU数220で、しかも第2世代のMatrix Coreを880個(つまりXCUあたり4つ)搭載。メモリもHBM2Eを合計で8スタック搭載する(Photo08)。

ちなみに第1世代のRadeon Instinct MI100の場合、TSMCのN7を利用しているが、XCUが120個(15×4×2)で、ダイサイズは筆者推定で763.2平方mmとなっている。TSMCのN7と比較した場合、N6は18%ほどトランジスタ密度が向上しているとされるし、XCU数が120→112と減っているから、2割強ダイサイズが減ってもいいのだが、その反面XCUそのものの強化やMatrix Coreの強化などもあるから、実際のダイサイズは700平方mm近いのではないかと想像される。これ以上のダイを作るのは露光サイズの限界があるから厳しいはずで、それもあってPonte Vecchio同様に2つのダイを搭載する、という方向に舵を切ったものと思われる。

さてこのDual Die+HBM2E×8のRadeon Instinct MI200だが、従来のCoWoSベースのSilicon Interposerに替えて、AMDは新しい2.5D EFB(Elevated Fanout Bridge)を導入してきた(Photo09)。

そのEFBの構造がこちら(Photo10)。

-

Photo10:左は要するにIntelのEMIBである。EFBのPillerは、要するにダイの裏のBumpの下にそのまま接続するような形で構築されるので、Interposerを使わない、外部に出す信号(や電源/GND)はそのままPiller経由で外部に引き出される格好になる

従来この手のものとしてはIntelのEMIBがある訳だが、こちらはベース基板に埋め込む形になるので、信号伝達特性は良いし高さは抑えられるものの、実装コストは高くつくものになっていた。これに対してEFBの場合、Silicon Interposerにあたるものをベース基板の上に置く形になる。ただそのままだと高さが合わないので、周囲に銅配線の柱(Piller)を立てて、ダイ全体を持ち上げるという技を利用している。この方式だと伝達特性は従来のSilicon Interposerと変わらず、それでいてEMIBに比べると遥かに安価で、しかも製造が容易という点がメリットとされている。CoWoSと異なり、Interposerの面積そのものは小さくて済むから、CoWoSと比較しても低価格で実装が可能になりそうだ。Radeon Instinct MI200では、ダイとHBM2E Stackの接続、およびダイ同士の接続にこのEFBを利用している。

さて問題はその性能であるが、AMDはRadeon Instinct MI200の性能をこんな風に紹介している(Photo11)。

これに同じAMDのRadeon Instinct MI100や、IntelのPonte Vecchioの数字も混ぜたのが表1である。Ponte VecchioはまだA0 Siliconの数字を拾っているところもあり、またFP64のMatrix演算が可能かどうかが不明などいくつか判らないところもある。

ちなみにIntelはPonte Vecchioのメモリ帯域を5TB/sec以上と説明しているが、そもそもHBM2Eが現状提供されているもので最大4.2GT/sec。ピン数1024本だから1 Stackあたりでも最大で525GB/sec。これを8 Stackにしても4.2TB/secにしかならない。帯域で5TB/secを超えるとなると、信号速度も5GT/secを超えるのだが、そんな製品はあるのだろうか? ちなみにRadeon Instinct MI200は3.2TB/secと控えめなのは、安定して動作する3.2GT/sec品を選択したためと思われる。

なお、Frontierに納入されるRadeon Instinct MI200は、従来のPCIeカードではなくOAM(OCP Accelerator Module)の形を取った製品(Photo12)となるが、同じくOAMのA100との実性能比較がこちら(Photo13)。

-

Photo12:OAMの仕様はこちらから入手できる。ただOAM準拠ということは、12V駆動だとTDPは350W以内という話になる(SpecificationのPage 47)のだが、どこまでこれを守っているのかは謎。あるいは48V駆動で、TDP700Wなのかもしれない

主要なHPCアプリケーションで、A100の2倍以上の性能を実現するとしている。またこのRadeon Instinct MI200に合わせる形でROCmも5.0がリリースされることが明らかにされた(Photo14)。

-

Photo14:原稿執筆時点ではまだGitHubには4.5 Releaseまでしか公開されていないが、間もなく5.0が公開されるものと思われる

そのRadeon Instinct MI200、実際の製品としてはOAMタイプが2製品(MI250X、MI250)のほか、PCIeタイプのカードであるMI210 PCIeも後追いで追加されることになっている。MI210についてはまだ細かな数字が出ていないが、MI250X/MI250は表2の様な構成になっている。おそらくFrontierにはMI250Xが導入されることになるかと思う。

さて現在Frontierには導入作業が進められている(Photo16,17)訳だが、そのFrontierの内部構成はこんな感じになるようだ(Photo18)。

この場合ノード辺りのピーク性能は、EPYCが例えばEPYC 7763に3D V-Cacheを搭載した構成だと仮定すると、ピーク性能そのものは3D V-Cacheの有無で変わらないから、Base Clock(2.45GHz)の場合でおよそ2.51TFlops(FP64)ほど。一方Radeon Instinct MI250XはFP64 Matrixで95.7TFlopsだから、ノード(CPU×1+GPU×4)あたりのピーク性能は385.3TFlops。Photo01で判るように2つのノードで1枚のブレードを構成しているから、ブレードあたりの性能は770.6TFlopsとなる。Photo16の図で見ると、1本のラックに32枚のブレードが入っている様に見えるので、という事はラック当たり24.7PFlops。1.5EFlopsを実現するには60ラック強で済む計算になる。

ただ実際には3ラックごとにサービスラック(SlingShot用だろうか?)が1つ入っているから、これを加味すると81~82ラック。あとはストレージなどの分を入れると100ラック程度というあたりか? 以前安藤先生がISC21におけるThomas Sterling教授の講演を紹介されたときに、Frontierが104ラックという数字が出ており、概ねこれに沿った形に見える。

なおAMDはこうしたハイエンドHPC向け以外に、メインストリーム向けの構成(Photo19)とかML向けにノードの規模を2倍にした構成(Photo20)なども提案している。

-

Photo19:やはり全部をInfinityFabricで繋ぐのはコスト的に上がるので、GPU同士あるいはCPU同士のみInfinityFabricとし、そのほかはPCIeで接続する事でコスト低減と柔軟性向上を狙ったと思われる

-

Photo20:PCIe Switchが結構な高価格になりそうな予感。ところでこのRadeon Instinct MI250×8の繋ぎ方は、かつてのOpteron 8Pを彷彿させる構成である。歴史は繰り返す?

Frontierが無事に稼働し、その性能が証明された場合には、当然AMD(というか、HPE)はこれのサブセットをもう少し安価に拡販する事を狙う訳で、Photo19はそうした場合に向けた構成と思われる。Photo20は「頑張ればここまで行けます」の例だが、果たして導入するようなところはあるのだろうか?