2021年も「PCI-SIG Developers Conference」はオンラインでの開催となった(PCI-SIG Virtual Developers Conference 2021)。これもあり、恒例のPress Conferenceも昨年に引き続きオンラインでの開催となっている。昨年に比べると、今年は大きな目玉となる話は無かったが、細かいUpdateがいくつかあったので、これをご紹介したい。

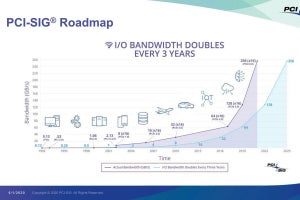

まず恒例のロードマップ(Photo01)。

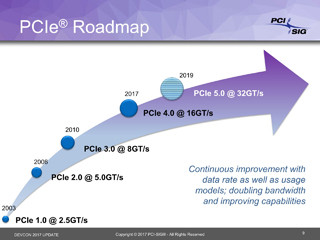

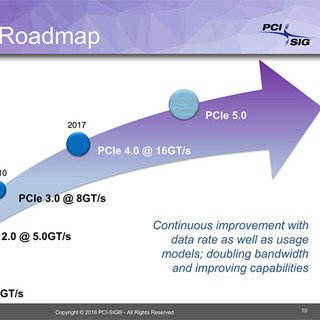

実のところ、やっとPCIe Gen 4が普及に入り、現在はPCIe Gen 5への対応を各社が水面下で進めているという状況ではあるが、逆に言えば2022年にはこのロードマップの通りにPCIe Gen 5が市場に登場するのは間違いなく、Gen 6の2025年というロードマップもプロセス(5nm~3nm)の進捗を見ている限りでは丁度このあたりに来そうな感じである。

今年の新たな話題は、オートモーティブへの参入である。実はオートモーティブへのPCIeそのものはすでに始まりつつあり、今年の4月にはBrightTALKでセミナーも開催されているのだが、ここでの話題はそこからもう一歩踏み込んで、機能安全に関する取り組みをPCIeの中に取り込もうという話である。

最初のターゲットはISO 26262 ASIL-B/Dあたりになると思うのだが、長期的にはそれこそIEC61508などの他の分野向け機能安全にも応用が効くだけに、機能安全向けのPCIe Solutionは重要と考えているようだ。すでにWorking Groupを立ち上げているという話であった。

6月16日に、これに関するセミナーも予定されているので、ここでもう少し細かい話が出てくるかもしれない。

次に進捗について。PCIe Gen 4に関してはもう2019年からCompliance Programがスタートしており、コロナの影響で2020年以降はちょっと頻度(というか規模)が控え目になりつつも着々と行われてきている。

これに対してPCIe Gen 5は現状まだTest Specificationの作業を行っている段階ではあるが、それでも2月には最初のTestが行われ、6月には2回目のTestが予定されているとする。

-

Photo03:まぁTest Specificationを完成させるためには、そのSpecificationの妥当性を実際にTestの場で検証する必要があるから、Specification完成までにはもうちょっと時間を要する模様

ただすでにBase Specificationなどは2019年にリリースされ、すでに多数のIPが7nm~5nmプロセスをターゲットに提供開始されている。当初こそVerification IPが多かったが、すでに主要なIPベンダーはコントローラあるいはデバイス向けIPを提供しており、これらを利用したSoCの開発も進んでいる。早ければ今年中にはPCIe 5.0を搭載する量産向けチップのEngineering Sampleが登場する予定(多分先鞭を切るのはIntelのSapphire Rapidsだろう)であり、これに向けてSpecificationの完成を急いでいるというあたりではないかと思う。

ちなみにPCIe Gen 5では、遂にChannel Insertion Loss Budgetが36dBに達している(Photo04)。

となると、PCIe Gen 4よりもさらに配線の引き回しには注意する必要がありそうである。Zen 4コアのRyzenで採用されるSocket AM5は、従来のPGAからLGAに変わるという話が出ているが(まだ真偽のほどは当然ながら明らかにされていない)、もしこれが事実であれば理由の1つはPCIe Gen 5対応だろう。

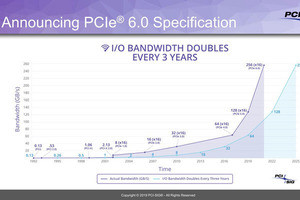

次がPCIe Gen 6の話。昨年11月にSpecificationのDraft 0.7がリリースされたが、Error Recoveryなどの追加のために新プロトコルが必要、という話になったそうで、これを追加したDraft 0.71が来月リリース予定である。0.7からの差分はこの新プロトコル周りだけだそうで、なので問題が無ければすぐにDraft 0.9に移行。ここから数か月を経て1.0になる、ということで今年の年末あたりにSpecificationが完成する予定である。

ちなみにこの6.0ではPAM-4エンコードと、これによるBER悪化を防ぐために軽量FEC+FLITを追加した、という話は昨年説明した通りで、特にここに関しては新しい情報はない。ただPhoto05左の一番下にあるように、TLPベースで新しいデータ暗号化が新たに追加されたようだ。

また今回説明はなかったが、3月に行われたオンラインセミナーのQ&AがPCI-SIGのBlogに掲載されており、この中でPCIe Gen 6ではx32レーンとx12レーンが削除されることが明らかにされた。x32レーンはそもそも誰も使わず、またx12レーンはInfiniBandからの強い要求で追加されたにも関わらず、昨今ではそのInfiniBandもx16レーンとかx8レーンばかりでx12レーンを使っていないので、どちらもサポートから削る事にしたそうだ。個人的には妥当な選択だと思う。