Lakefieldのスペックで未だ不可解な部分

2018年のIntel Architecture Dayで初めてその名前が出てきたLakefield。ただこの時は10nmで製造されたCoreと14nmで製造されたAtom+I/OをFoverosで立体化するという話で、まだコンセプトモデルに近いレベルの話であった。ただある意味これは目くらましであって、2019年のCESではかなり現実に近いモデルに切り替わった。その後、Sunny Coveの詳細やTremontの詳細も明らかにされた訳であるが、既に2製品がark.intel.comに登録されており、プレスリリースよりも詳細なスペックが公開されている。

表3はこれをまとめたものであるが、実は搭載メモリは4GBと8GBの2種類のSKUがあること、及び価格はCore i3/i5、4GB/8GBを問わず一律$281.00なことなどは普通にスペックを見ただけでは判らない仕組みになっている(価格は現時点では見られなくなっているので注意)。

| ■表3 | ||||

| Processor Number | i5-L16G7 | i3-L13G4 | ||

|---|---|---|---|---|

| CPU | コア/スレッド数 | 5/5 | ||

| キャッシュ容量 | 4MB | |||

| 動作周波数(GHz) | 定格 | 1.4 | 0.8 | |

| 1コア最大 | 3.0 | 2.8 | ||

| 全コア最大 | 1.8 | 1.3 | ||

| Memory | 種別 | LPDDR4X-4267 | ||

| 容量 | 4/8GB | |||

| バス幅 | 64bit | |||

| Graphics | EU数 | 64 | 48 | |

| 動作周波数(GHz) | 定格 | 0.2 | ||

| 最大 | 0.5 | |||

| TDP | 7W | |||

| 推奨小売価格 | $281.00 | |||

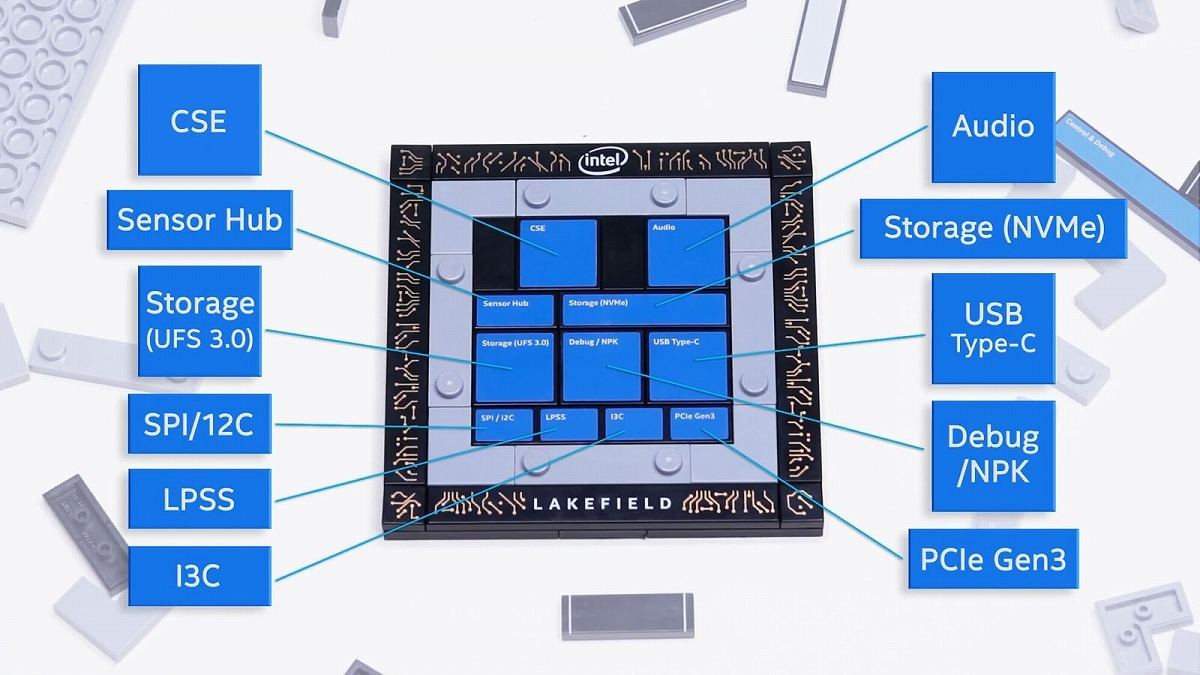

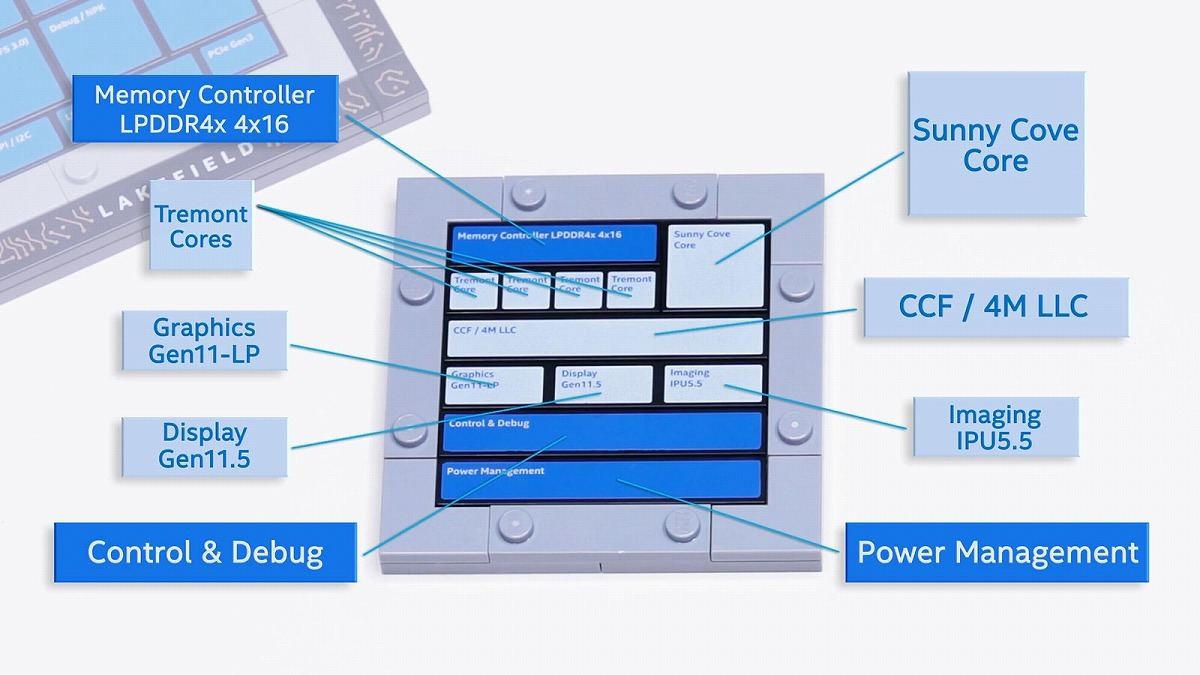

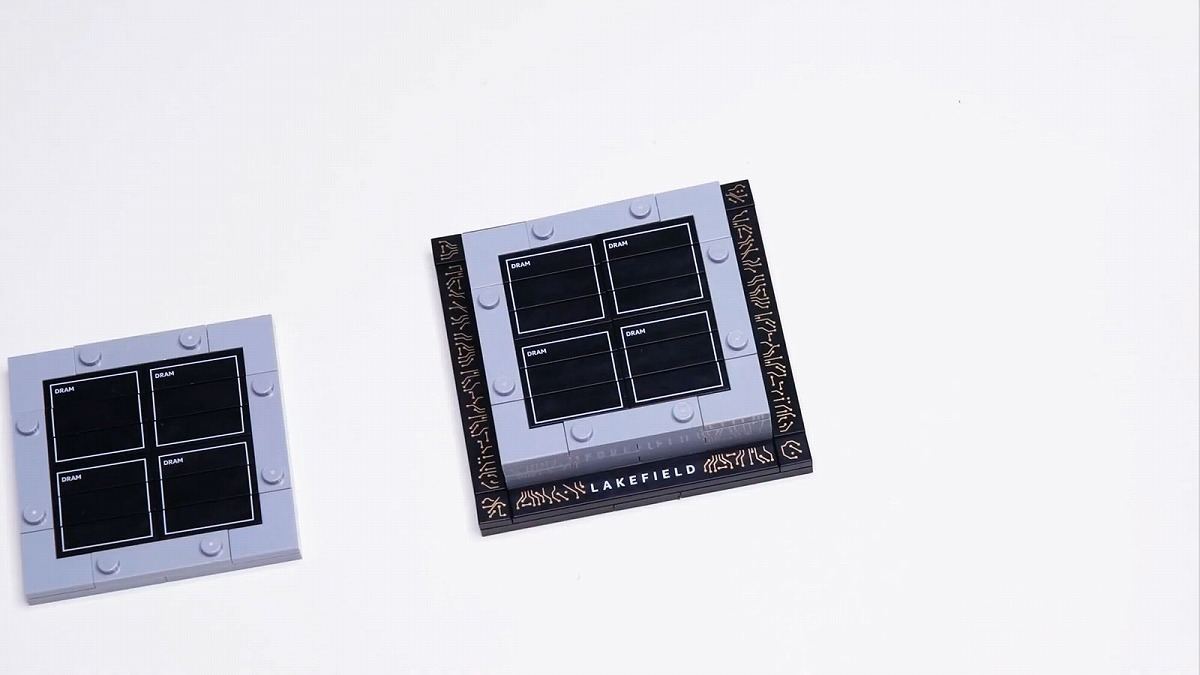

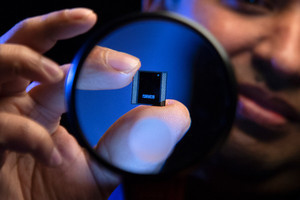

それはともかくとして、まずメモリについて。IntelはLakefieldの発表に合わせ、LEGOでLakefieldを作るという動画を公開しているが、これを見るとまずI/O Die(Photo03)、次いでProcessor Die(Photo04)と来て、次にDRAMが4つ搭載された層を「2つ」作り(Photo05)、しかもこれを積層している(Photo06)。という事はLPDDR4を最大8つ搭載できる? という事になるのだが、これは辻褄が合わない。昨年のInvestor Meetingの際のスライドでもDRAMは4つしかないからだ。また、LPDDR4xのI/FはPhoto04にもあるように、4×16bit構成である。現在のDRAMトップベンダー3社(Samsung、SK Hynix、Micron)はLPDDR4xに関しては16bit幅が一番小さい構成であり、8bit幅の製品はリリースしていない。となると、メモリを2層積層してもそれを利用する方法がない。

可能性としては

- スペシャルでx8構成のLPDDR4xを作ってもらい、2段積層の場合はこれを利用する

- 実はMemory I/Fは4×32で、ただし最初のリリースはこのうち4×16しか使わない

- 将来は2段積みを考慮するが、現状は未対応

- ただのジョーク

あたりで、3番目か4番目の公算が非常に高い気がするのだが。とにかくMemoryに関してはそんな訳でちょっと不可解である。ただとりあえず今回発表された2製品に関しては、LPDDR4xが4つという構成は間違いない様だ。

次がCPUコアにまつわる話。表3にもある様に、例えばi5-L16G7なら全コア最大が1.8GHz、1コア最大が3GHzとなっているが、おそらくTremontコアはこの1.8GHzが最大で、これを超えられるのはSunny Coveコアだけという設定になっていると思われる。まぁそれはいいとして、面白いのはこれが5コア5スレッド構成になっている事だ。つまりSunny CoveとTremontはどちらもHyper-Threadingが利用可能にもかかわらず、これを無効化していることになる。

もう一つ面白いのが拡張命令。TremontはSSE 4.2までのサポートであるが、その代わりに新しくCrypto accelerationとかGFNI(Galois Field New Instructions)が追加された、という話はこちらで紹介した通りだ。一方で、Sunny CoveはGFNIこそないもののAVX512までのサポートがある。ではLakefieldは? というと、この両者の最大公約数を取った形になった。つまり拡張命令はSSE 4.2までで、AVXもGFNIも無しである。

なんでこんなことになったか? 筆者が考えるに、これはWindows 10のスケジューラ絡みの問題である。やはりここで書いた通り、MicrosoftはSnapdragonベースのArm SoCにWindows 10 on Armを載せる過程で、Armのbig.LITTLE/DynamIQをスケジューラでサポートしている。そしておそらくこのスケジューラをそのままLakefieldに応用するのではないかと予想したが、これが予想通りだったという事だ。というのはbig.LITTLE/DynamIQは

- 最大でも8コアまで、世の中にはこれを超えて10コア搭載のSoCもある(古い所ではMediatekのHelio X30)が、これに関してはそのベンダーが独自のスケジューラを提供する(MediaTekの場合はCorePilotと呼ばれる独自スケジューラが用意される)ことで解決しており、一般的ではない。Qualcommはこの点に関してはArmのガイドラインに従い、最大8コアまでの製品しか出しておらず、Windows 10 on Armの実装も当然これに則ったものになる。

- 同一命令セットが必要 big.LITTLEにせよDynamIQにせよ、サポートする命令セットは完全に同一である必要がある。つまり命令によるスケジューラのDispatchは行われない。

という2つの制限がある。今回、Hyper-Threadingを無効化したのも、これを有効化すると10コア相当になってしまい、8コア制限を超えてしまう事になる。また対応命令セットを最小公約数的に設定したのも、これが理由に思える。

逆に言えば、これはWindows 10ベースでMicorosftの提供するスケジューラを使う限り避けえない話になる訳だが、それ以外の、例えばLinux向けのスケジューラを自身で手を入れれば、このあたりの制限が回避される可能性がある。もっとも、そうしたニーズがどこまであるのか、という話ではあるのだが。これは次のバリエーションの話に繋がる。

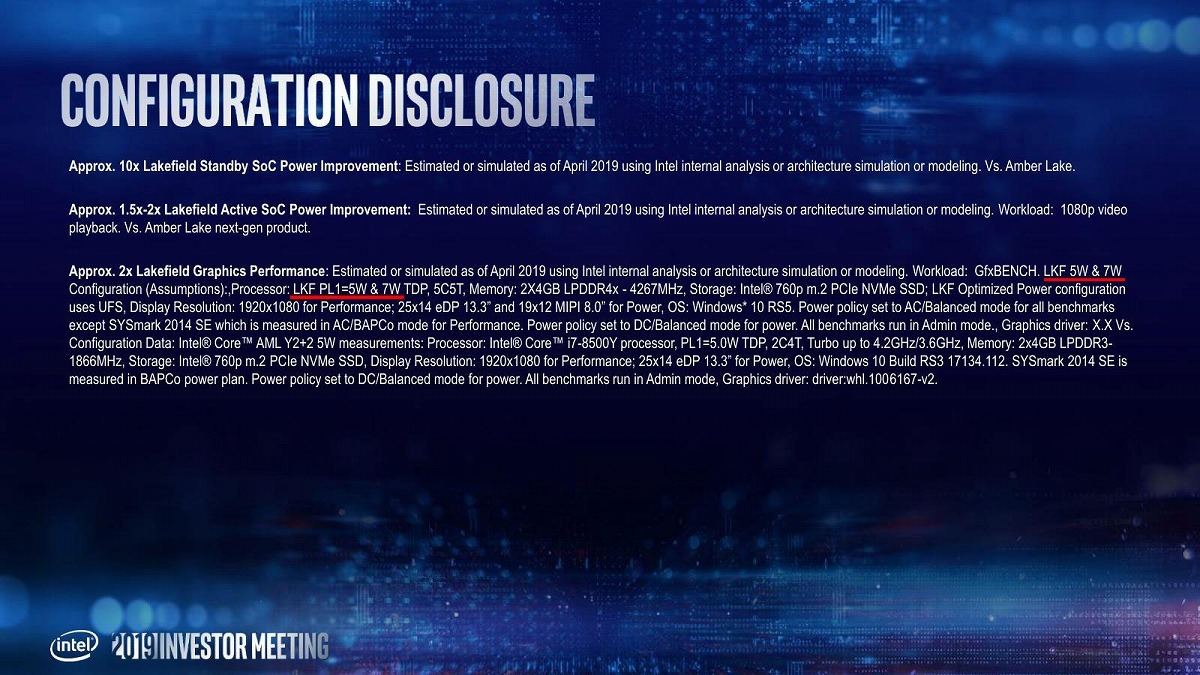

そのバリエーションの話。今回はTDP 7Wの製品が2つ発表されただけだが、少なくともTDP(というか、PL1)が5Wの製品が予定されていたことはこちら(Photo08)からも明らかである。ちなみに現在のLakefieldのPL2がどの程度かは現状未公開(9.5W、という数字が流れてきているが、確定情報ではない)である。

で、これで終わりか? というと良くわからないのだが、可能性的にはより消費電力を引き上げた製品があっても良さそうに思える。現状の7WというのはY SKUに相当する訳だが、U SKUは狙っても問題ない気がする。PL1が15W、PL2が25~27Wというカテゴリーだ。なんでそう思うかと言えば、ハードウェアを変えないままでも例えば

- Sunny CoveのHTを有効にして、2+4コア構成

- TremontのHTを有効にし、ただしコアを半分無効化して1+4コア構成

にすれば、前者は7Wの枠ははみ出すにしてももう少し性能が上がるし、後者は性能こそ落ちるが消費電力は更に落ちるだろう。Pentium/CeleronグレードのLakefieldが必要になった場合には後者の構成が役に立つはずだ。

またLakefieldでは現状、異様にGPUの動作周波数が低い。定格200MHz、Turboでも500MHzというのは、ダイサイズを考えるとかなり無駄が多い。実際この周波数なら、EU数を半減させ、動作周波数を倍にしても恐らく消費電力は変わらない筈だ。ただ、仮にTDP 15W枠になって動作周波数を引き上げるとなると、話が変わる。15W枠なら700~800MHz程度まで動作周波数は引き上げられるだろう。この範囲だと、まだ消費電力が急増はしないからだ。ただこれを倍速(1.4~1.6GHz)で動かすとなると、消費電力がグンと跳ね上がると思われる。多分Lakefieldの64EU構成は、1GHzを超えない範囲で使う事を前提にデザインされたのだろう、と想像される。現在はこれをY SKU相当の7Wで動かしているから妙に動作周波数が低いが、本来はU SKU相当の製品を念頭に考えたのではないかと筆者は予測している。

もっともそうした製品が本当に世に出るかどうかは未知数である。とにかくスケジューラ周りが厄介というのが実情であり、はたしてSurface Neoに続く製品がどこまで出てくるか。その意味ではどこまでSurface Neoが売れるか次第で決まるのかもしれない。