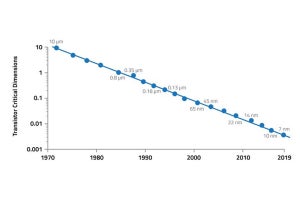

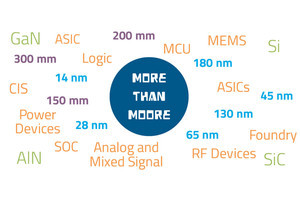

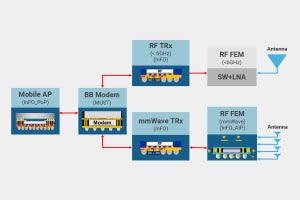

IC設計者がより小さな面積に、より高度なチップ機能を盛り込む中で、デバイスの3D積層技術をはじめとするヘテロジニアスな集積化は、様々な機能や技術を組み合わせて活用するための有用かつコスト効率に優れた方法となりつつあります。そうして採用が進んでいるヘテロジニアスなインテグレーションプラットフォームの1つが、高密度の「ファンアウト型ウェハレベルパッケージング(FOWLP)」です。このパッケージングソリューションの主なメリットとして、基板レスパッケージや、熱抵抗の低さ、電気性能の向上などがあります。これは、純粋なムーアの法則による微細化以外の技術がさらなる集積度と有利な経済性をもたらす、「More than Moore(モア・ザン・ムーア)」のプロセスの一例です。

ヘテロジニアス・インテグレーション手法

高密度のファンアウト型パッケージングは、携帯電話用パッケージングのフォームファクタと性能の要求に応えるものとして勢いを増しています。この技術の主要構成要素には、再配線層(RDL)金属やメガピラーのめっきなどがあります。RDLは、シリコンチップ上の高密度の接続を、プリント基板上の密度のより低い接続にルーティングするのに使用されます。基板への信号ルーティングを可能にするためには、複数のRDL層が必要です。

図1のとおり、メガピラーは各層をつなぐ金属の垂直の接続部です。上部のダイからのはんだバンプがメガピラーの上に置かれ、リフローはんだを利用して接続がなされます。

メガピラープロセスにおける課題

メガピラーはそのサイズに特徴があり、標準的な銅ピラーに比べて約5倍の高さと幅があるのが一般的です。メガピラーを形成する昔ながらのアプローチは、従来の電解めっきを使用することです。これは時間のかかるプロセスですが、最大の問題は、このプロセスでは通常、許容範囲を超えて均一性が悪くなることです。電解めっきされたメガピラーは、局所的な電流密度の違いで、高さがまちまちで、メガピラーの上部に望ましい平坦な表面が形成されず、一定レベルのドーム形状やディッシングが生じる場合があります(図2)。

高さと形状の不均一さから、平坦化の追加プロセス(CMPなど)が必要となり、デバイス性能を劣化させる信頼性の低い接続や、全体的なプロセス時間とコストの増加につながってしまいます。

こうした電解めっきの結果に影響を及ぼすダイレイアウトのばらつきには、形状、幅、アスペクト比、周囲のフォトレジストの厚さ、任意の範囲のパターン密度などがあります。それらの差異が生じるものとしては、ウェハ、ダイ、あるいは個々のパターン間の距離があります。

この問題を解決する方法の1つは、目標とする厚さを超える量の金属をめっきして、その後にめっきの分極と電流を反転させることです。それにより、追加した金属をエッチングし直して高さ分布を狭めるか、メガピラーの上部を平坦なままにします。しかしこのアプローチは、様々な長さにわたって均一性を向上させるのに効果的ではない場合があり、しばしば表面モホロジーの悪化を生じさせるため、メガピラーの表面は穴やエッジ腐食のある粗いものになってしまいます。

ウェハ全体でメガピラーの高さを均一にする技術

Lam Researchはこの問題に、「Durendal」という独自のプロセスを提案しています。Durendalは、メガピラーの上部に高品質かつ平らな表面を形成し、ウェハ全体でメガピラーの高さを均一にします。Durendalの全体のプロセスは、SABRE 3Dで実行されます。

Durendalプロセスは、ダイスタッキングにおける経済的な方法であり、歩留まりに優れた堅実で信頼性の高い接続を実現します。ダイスタッキングのパッケージング手法としてFOWLPの採用が進むにあたり、Lam Researchは将来的にDurendalプロセスが大きな役割を果たすものと期待しています。

著者プロフィール

スティーブン T.メイヤー (Steven T. Mayer)Lam Research

Fellow

先進ウェットプロセスの研究開発を指揮

ブライアン・バッカリュー (Bryan Buckalew)

Lam Research

技術ディレクター

ウェット装置/技術ソリューション関連を統括

カリ・ソルケルスソン (Kari Thorkelsson)

Lam Research

成膜製品グループ シニア・プロセスエンジニア

パッケージの電気めっきに従事