AMDが開催したプライベートイベントNext Horizonのレポートの続きとなる。CPU編から時間が空いてしまったが、GPU編ということでVega 7nmについてもDeep Diveをお届けしたい。

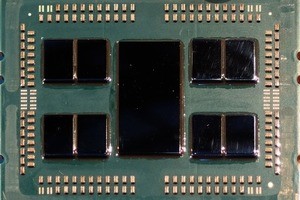

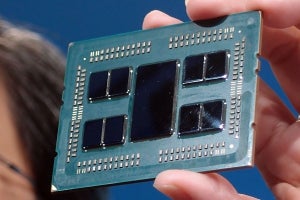

こちらもZen 2と同じく、TSMCのN7を利用することで、高密度化と高性能化/省電力化を図ったとする(Photo01)。Vega 10ベースのRadeon Instinct MI25とVega 20のRadeon Instinct MI60のダイを比較したのがPhoto02である。

ただし、ダイのスペックを比較すると

| GPUコア | Vega 10 | Vega 20 |

|---|---|---|

| トランジスタ数 | 125億個 | 132億個 |

| ダイサイズ | 487平方mm | 331平方mm |

となっており、トランジスタ数が若干増えたことを勘案しても、トランジスタ密度は1.55倍程度に留まる。この理由はPhoto03を見ていただくとわかりやすい。

シェーダが実装されているとみられる赤枠の面積は、Vega 10の方が推定で375.3平方mm、Vega 20の方は203.9平方mm程度になっている。ここだけ比較すると、2倍とまではいかないまでも84%ほどトランジスタ密度が上がっている。

後述するが、シェーダの内部構造に追加機能があるから、実質的にはほぼ倍に近いトランジスタ密度を実現できていることは間違いなさそうだ。Photo03で見ると、ダイの中にかなりの無駄な領域が確認できる。それにもかかわらず、これ以上小さくできないのは、HBM2への配線の関係と思われる。

Photo04を見ると、HBM2のStackを縦方向にこれ以上縮めるのは難しい。そのHBM2への配線を最短にしようとすると、2つのHBM2 I/Fの縦方向の距離を詰める必要があるが、これもかなり難しい。結果的に、かなりゆとりのあるダイレイアウトになってしまっている。その結果が、この300平方mmを超えるダイということだろう。

ただ、もう一度Photo02に戻ると、Vega 10とVega 20で、中央部の配置こそ若干違うものの、基本的には極めて相似したレイアウトになっている。中央部はACEやHWS、それとL2が実装されていると思われるが、Vega 20の配置であればこうしたものをもう少し左右に追いやることで、NCUの数をもう少し増やすことも可能だろう。

もしくはNCUの内部構造を見直して、幅をもう少し狭める(その分高さを増やす)と、ダイの横幅を削減できると思われる。そうした策を取らず、ほぼVega 10と相似形になっているというのは、ことVega 20に関しては「最適化の度合いが低い」というか、もうRadeon Instinct(とおそらくRadeon Pro)向けにしか利用しないつもりなのかもしれない。

そうであれば、あまり最適化に時間を掛けるよりも、次の設計に早めに取り掛かるほうが得策、と割り切ったのではないかという気がする。

ただこの結果として、Vega 20の原価はVega 10に比べて結構高くなっていると想像できる。設計コストは除外するとしても、ラフにいって7nmのウェハは12/14nmウェハの倍近い製造コストになる。

そのため、Vega 20のダイはVega 10に比べて30%くらい製造原価が上がっていると考えられる。おまけにHBMの数も倍になっているわけで、トータルとしてのコストは倍にはならないにせよ、5割増し位になっていても不思議ではない。こうなるとコンシューマ向けにもってくるにはかなり厳しいという位置付けになるだろう。

余談だがEPYCのコスト感は? というと、パッケージは別に考えるとして、Summit Ridgeのダイのコストを100とすると、EPYCはこれが4つ実装されているので400だった。これがEPYC 7nmの場合、CPUダイは1個あたり65程度で、これが8つで525程度。I/Oダイが大体200程度で合計で725程度となる。

つまり、原価は80%増しだが、性能は100%増しになるわけで、トータルではコスト/パフォーマンスが改善されるという結果だ。Vegaではどうか?という話を次に。