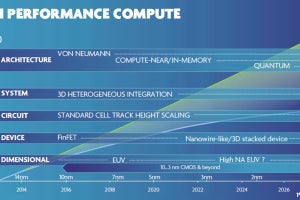

ベルギーimecは、米国ハワイで開催された半導体デバイス・回路技術の国際会議「2018 Symposium on VLSI Technology and Circuits(VLSI Symposium)」にて、合計14件の講演を行い、3nmプロセス以降の微細化技術に関する研究などを発表した。

3nm以降の微細化に適した相補型FET

imecが発表した、3nm技術ノード(N3)を超えた微細化のための相補型FET(CFET)のプロセスは、最終的にFinFETより優れた性能を示し、消費電力と性能面でN3の要件を満たすことができ、スタンダードセル(SDC)とメモリSRAMセルの専有面積を50%拡大することができるとしている。

CFETは、垂直(縦型)ナノワイヤトランジスタをさらに進化させた構造である。 n型デバイスとp型デバイスをそれぞれ別々に積み重ねる代わりに、両者を重ねて一緒に積層する。p型フィン上にn型縦型シートを積み重ねる構造である。

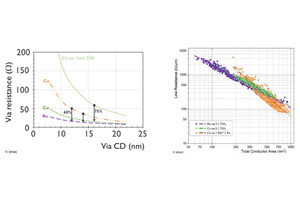

これにより、従来のFinFETフローを活用し、ボトムのpFETの歪み効果を生かせる。TCAD分析に基づいて提案されたCFETは、電力と性能の点でN3の目標を満たすことができ、FinFETより、消費電力、性能の点で優れているという。しかし、解決せねばならぬ問題があった。それは深いビアの寄生抵抗をいかに低減するかである。これについては、ルテニウム(Ru)を用いたMiddle of Line(MOL)コンタクトを導入することで達成することができたとしている。

「優れた電気的特性を有し微細化に向いているCFETデバイスは、N3以降に必要な新しいデバイスアーキテクチャの優れた候補であり、ムーアの法則の終焉をさらに遠ざけることができる」と、imecのCFET開発担当者Julien Ryckaertは述べている。

歪みGeナノワイヤFETで5nm以下の微細化を実現

また、5nmプロセスを下回るような微細化を実現するための実用的解決策としてGeナノワイヤp型FETデバイスについても2件の論文が発表された。1つ目の論文では、従来のSiに代わる歪みGeナノワイヤpFETの電気的特性について詳しく調べた結果が紹介されたほか、もう1つの論文では、横型に配置されたゲートオールアラウンド(GAA)構造の歪みGeナノワイヤpFETについての報告が行なわれた。

これらの論文について、imecの半導体技術およびシステム研究開発部門のEVPであるAn Steegen氏は、「半導体産業界は、さまざまな微細化技術を駆使して、FinFETを7nmや5nmに延命できるだろう。ただし、それ以降のデバイスでは、GAA構造が実用的な解決策になると見ている。GAAを採用すればFinFETプロセスの多くを再利用できるからである。しかし、GAA構造を実現するために横型ナノワイヤを用いると、チャンネル断面積が、FinFETに比べて狭くなってしまうという問題がある。単位面積当たりの電流駆動力を改善するためには、この横型ナノワイヤを縦に積み上げる必要がある。そうすると、寄生容量や寄生抵抗が増してしまう。この問題を解決するには、SiナノワイヤをGeのような高移動度チャンネル材料で置き換えて単位面積当たりの駆動電流を増加させることである。今回の研究により、5nmを下回る微細化デバイスの製造コストや面積や性能の要求にこたえられることが明らかになった」と今回の成果を説明している。

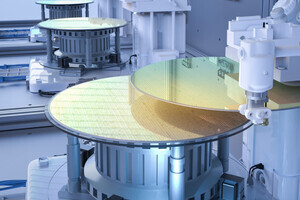

300mmウェハ上で先端SOT-MRAMの製造可能性を実証

このほかimecでは、CMOS互換プロセスを用いて300mmウェハ上で先端技術であるスピン軌道トルクMRAM(SOT-MRAM)デバイスを作製することに成功したことも報告している。

imecでは、この次世代MRAM技術を、高性能コンピューティングアプリケーションにおけるL1/L2 SRAMキャッシュメモリを代替するもの、と位置づけて研究開発を続けており、今回実現されたデバイス性能としては、500億回以上というほぼ無制限ともいえるスイッチング耐久性、210psのスイッチング速度、300pJの低消費電力性といったものが確認されており、これらは、これまでに報告されたいる実験室レベルでのデバイス特性に匹敵するものだという。

SOT-MRAMは近年、STT-MRAMの限界を超えることができる次世代メモリと期待されるようになってきたが、実験室での研究が主で、300mmウェハを用いた研究や試作はほぼ行なわれてこなかったという。今回の流れは、そうした取り組みの一環で、磁気トンネル接合は、垂直に磁化されたSOT/CoFeB/MgO/CoFeB/SAFの積層構造、SOT層にベータ相のWを用いて300mmウェハ上に製作されたSOT-MRAMと、従来のSTT-MRAMのスイッチング速度を比較したところ、SOT-MRAMが210ps、STT-MRAMが5nsと、大きな性能差が示されたとする。

なお、imecの技術スタッフであるGouri Sankar Kar氏は「STT-MRAMの技術は、高性能コンピューティングアプリケーションでL3キャッシュメモリを置き換える可能性が高い。しかし、より高速さが求められるL1/L2 SRAMキャッシュメモリを置き換えるには不適切である。一方でSOT-MRAM技術は、MRAMの動作をSRAMアプリケーション領域に拡大するのに役立つと期待されており、今回、実際に300mmの試作ラインへ移管させることで、技術の成熟度を実証できた」と説明しているほか、「今後の研究では、電流密度を低下させ、フィールドフリー・スイッチングを実現してエネルギー消費をさらに削減することを目指す」とし、さらなる研究開発を進めていくとしている。