米Lattice Semiconductorは5月21日(米国時間)、同社のFPGA「iCE40 UltraPlus」および「ECP 5」上で稼動するBNN/CNN用のIPと、これを利用するための開発環境をパッケージ化した「sensAI」を無償提供することを発表した。このsensAIについて、同社は5月25日に都内で記者説明会を実施し、詳細を明らかにした。(Photo01)。

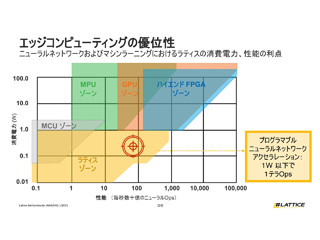

今回発表されたsensAIは、2018年2月に開催されたBillerbeck元CEOの説明会で示されたAIベースの顔追跡技術や、AIベースの顔認証、あるいは2017年11月に開催されたGlen Hawk元COO(2018年5月時点では暫定CEO)の説明会におけるエッジコンピューティングで実現可能な低消費電力ニューラルネットワークアクセラレーションの話そのものであって、その意味では目新しさそのものは無い。ただし、今回はその内部の詳細が語られたこと(Photo02)、ならびに対応したソフトウェアツールといった点で更新がなされた(Photo03)。

-

Photo02:iCE40のBNNの方は、内蔵の1Mbitのメモリで全部まかなう必要がある関係で、Convolutionは最大2つとか。対してECP5の方は外部メモリを利用できるので、Convolutionを最大8つまで並行で実行できるとの事

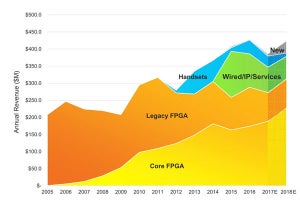

いささか話が逸れるが、もともと同社はスモールビジネス志向を貫くのが戦略であり、積極的にグルーロジック向け用途に入り込む方向性をとっていた。ただし、そうなると必然的にRTL(というか、HDL)を使ってコードを記述する必要がある。ところが今回の特徴は、RTLを得意としない(というか、書けない)エンジニアが同社のFPGAをアクセラレータとして利用するためのツールとして構成されていることだ(Photo03)。

-

Photo03:今のところ対応するフレームワークはCaffeおよびTensorFlowであり、Caffe2(3月末に「PyTorch」にマージされてしまった)には未対応との事であった

これは同社としてはある意味、初の試みである。このあたりを端的に示したのが以下の図(Photo04)で、従来の様にLattice DiamondあるいはLattice Radiantを使ってRTLで記述したものをビットストリーム化してFPGAにロードするという開発手順とまったく異なる、学習済みネットワークを(Photo03に出てきた)ニューラルネットワークコンパイラに掛けて、そこからFPGAのビットストリームを生成するという新たな開発パスを提供するという話である。

こうした方向性の転換は他のFPGAベンダも同じであり、XilinxはSDxxxシリーズ、Intel(旧Altera)はFPGA SDK for OpenCLやSoC EDS(Embedded Design Suite)が、それに相当する。ただし、FPGA SDK for OpenCLはともかくその他のソリューションが大体有償提供なのに対し、sensAIは無償で提供されるというスタンスを採用したあたり、これまで同社のFPGAを使ってこなかった開発者にリーチするための手段、という位置づけが強いようだ。つまりグルーロジックから専用アクセラレータへの転換、という戦略のための呼び水とでも言うべきであろう。

もちろんそうなると、開発力が十分でない顧客(つまりこれまでFPGAを扱ってこなかった開発者)もターゲットとなるし、また逆にFPGAには慣れているがBNN/CNNには不慣れ、という開発者も考えられる。そうした開発者向けに、認定パートナー5社によるカスタムデザインサービスも提供するとする(Photo05)。

-

Photo05:これらのパートナーは、ニューラルネットワークそのものの開発や学習、FPGAへの実装、ターンキーソリューションの提供、と開発者のニーズにあわせたサポートを提供できるとする。新規の開発者がターゲットとあれば、こうしたフォローアップは欠かせないだろう

このほか、説明会ではiCE40 UltraPlusとECP5の両方のデモも行われた(Photo06~10)。

-

-

-

Photo07:iCE40 UltraPlusを搭載したMDP(Mobile Developemnt Platform)を使っての顔認識デモ。人差し指の先にあるのがiCE40 UltraPlus、その右にある黒い部品がカメラ。顔を認識するとLEDが点灯するというデモである

-

Photo08:65mile/hの標識認識デモ。左の棒グラフが確率で、高いほど高確率ということになる。6と5の数字がある関係で、45mile/hあるいは60mile/hもそこそこの確率にはなっている

-

Photo09:標識以外の画像が混じっていても、きちんと認識できる

-

Photo10:15mile/hの標識は学習済リストの中に含まれていないとのことで、どの速度の確率も低めになっている

FPGAを活用するのにRTLが不要な時代が到来

さてこのソリューションだが、Photo02にもあるようにあくまでもアクセラレータである。そのため、実際にはこのほかにホストとなるMCUなりMPUが必要になるのだが、このあたりが現状ちょっとうまく行ってないのが気になるところだ。

LUT数にゆとりがあるECP5はともかく、iCE40 UltraPlusの方は結構ぎりぎり(BNN AcceleratorのIPだけで3KほどLUTを消費するので、2800LUTのUP3Kでは乗り切らず、5280LUTのUP5Kが必須になる)となる。それでも2000LUTほど余る計算にはなるのだが、この程度のLUTではCPUを載せることが出来ない(同社のMico32はそもそもiCE40に載らないので、載せるとなるとRISC-Vになるのだが、これがぎりぎりLUTが足りないという話。そのためMCU+FPGAという2チップ構成になるか、もしくはsensAI以外の部分はRTLで記述して載せるということになる。前者は当然BOMコストや実装面積、消費電力の増大につながるし、後者はsensAIの存在意義が問われかねない。解決策はLUTの数を増やすことだが、これは以前アナウンスのあったSamsungの28nm FD-SOIプロセスを使った製品になる模様。もっともこのときの話では2018年中に出荷予定だったのが、直近で言えば2019年以降の出荷予定へとずれ込んでいるそうだ。いっそCortex-M0でも何でもいいから汎用のMCUコアをHard IPの形で搭載してくれれば話は楽なのだろうが、そうすると規模的にはMicrosemiのSmartFusion 2並になりかねないので、低コストを狙う同社としては難しいのだろう。

なお、今回の試みは同社としても初のものであり、顧客の反応を見て今後の方向性をまた検討していくようなので、このあたりは今後また違った展開になっていく可能性もある。なんにせよ、LatticeですらRTLを書く以外のFPGA開発手段を提供する時代になってきた、という意味で象徴的なソリューションと言えるだろう。