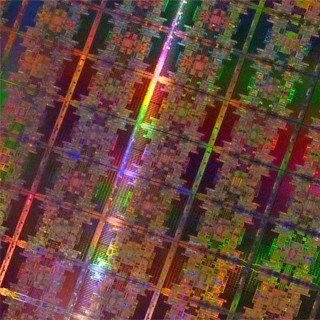

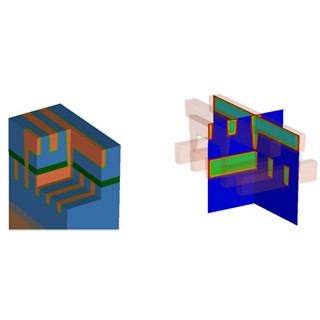

独立系半導体・ナノテク研究機関のベルギーimecは、米国カリフォルニア州サンフランシスコで開催された「International Electron Devices Meeting 2016(IEDM)」にて、ゲートオールアラウンド(Gate All Around:GAA)シリコンナノワイヤMOSFETを垂直に積層したCMOSトランジスタを発表した。

imecは2016年6月にハワイで開催された「VLSI Symposium」において、直径8nmのシリコンナノワイヤを垂直積層したFinFETを発表していたが、そこではn型FETとp型FETは別々に構成されCMOS構造にはなっていなかった。

今回の縦型GAAナノワイヤCMOSトランジスタは、業界初の成果とimecは説明しており、現在主流になっているFinFET構造を用いた7nm以降のCMOSトランジスタ構造の微細化に道を開いた形となる。n型およびp型デバイスのスレッショルド電圧を独立して制御するために、p型およびn型FETに、それぞれ仕事関数の異なる金属ゲート材料を適切に選択したことが成功の鍵となったとのことで、今後は、接合とナノワイヤ構成を同時に最適化するなどすべてのプロセスを最適化して実用化を目指すとしている。

なおimecは、同社のコアCMOSプログラムの傘下企業であるGLOBALFOUNDRIES、Huawei、Intel、Micron Technology、Qualcomm、Samsung Electronics、SK Hynix、ソニーおよびTSMCとの協業でこの研究を進めているという。