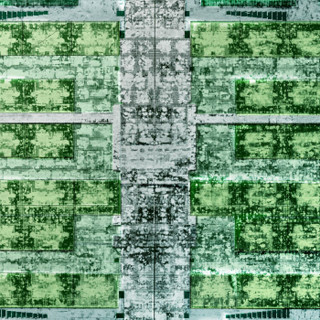

2016年6月に、フランクフルトで開催されたISC 2016において、富士通はポスト京コンピュータのプロセサをARMアーキテクチャにすることを発表した。しかし、この時はHPC向けのアーキテクチャの中身は発表されず、8月のHot Chipsで発表するというアナウンスだけであった。

その待望のARMv8-AアーキテクチャのHPC向け拡張をARMのリードISAアーキテクトでフェローのNigel Stephens氏が発表した。

|

|

ARM v8-Aアーキテクチャのスケーラブルベクトル拡張について発表するARMのNigel Stephens氏 |

ARMv7(AArch32)のAdvanced SIMD(NEON)命令は12年前のものである。AArch64のAdvanced SIMDもその発展形であり、本格的なHPC向けの命令セットにはなっていない。このため、HPC分野向けには、スキャッタ/ギャザーをサポートし、より長いベクトルを扱える命令を追加することが必要と考えたという。

そこで、サポートするベクトルの長さは128bitから2048bitの範囲で、128bit単位で自由に選択してハードウェアを作ることができ、一方、ソフトウェアは、ハードウェアのサポートするベクトル長に影響されない(Vector Length Agnostic)プログラミングができるようにすることができるアーキテクチャを考えた。このアーキテクチャを「Scalable Vector Extension(SVE)」と呼んでいる。

SVEでは、32本のベクトルレジスタZ0~Z31とスケーラブルなプレディケートレジスタP0~P15とFFRレジスタ、ベクトル長を指定する3つのZCR_ELxレジスタを追加している。

Z0~Z31レジスタは、NEONのV0~V31レジスタの長さを拡張する形で作られた128bitの整数倍の長さのレジスタで、64bitの倍精度浮動小数点数、32bitの単精度浮動小数点数と64/32/16/8bit長の整数を格納することができる。P0~P7レジスタは演算やロードストアの実行を制御するレーンマスク、P8~P15はプレディケートを操作するためのレジスタである。そしてFFRはFirst Fault Registerで、最初にフォールトが起こった命令を指すレジスタである。

ZCRレジスタは特権レベルごとにレジスタがあり、それぞれのレベルの処理のベクトル長を指定する。

AArch64では、命令語の28:25bitが命令の大きな種別を表している。この部分が0000、0001、0010、0011の4つの命令は現在は未使用であるので、0010をSVE系の命令に割り当てることにする。

そして、命令の中分類には31:29と24の4bitが使われており、SVE系の命令の場合は、次の表のように割り当てる。例えば、0000は整数の演算命令、0111は浮動小数点の演算命令と比較命令となっている。そして、100xはギャザー付きの32bitロード命令となっている。

なお、HPCでは32bitアーキテクチャは重要ではないので、AArch32へのSVE拡張は行っていない。

SVEの各命令の詳細やソースやディスティネーションのレジスタ番号の指定に使えるのは、24bitである。データのサイズやプレディケートの指定のビットが必要であるので、2つのソースオペランドと1つのディスティネーションのレジスタの番号を指定するのには24bitでは足りない。

このため、大部分のSVE命令では、結果がソース1のレジスタを上書きする2アドレス命令となっている。ただし、MOVPRFX命令とADD命令を連続して書くと、実質的に結果を別のレジスタに格納する3アドレス命令として動作するという仕掛けが組み込まれている。京コンピュータのSPARCプロセサでは、このような命令が設けられていたので、この部分は、富士通の貢献の1つではないかと思われる。

Hot Chips 28 - HPCへの進出を目論むARMのベクトル命令拡張(後編)はコチラ