2:imecは縦型GAAナノワイヤFETも同時発表

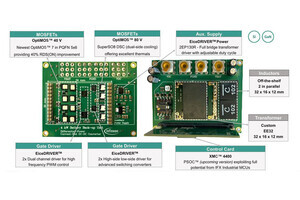

imecは今回のVLSIシンポジウムで、縦型のゲートオールアラウンド(GAA)ナノワイヤFETも同時に発表した(図2)。縦型GAAナノワイヤFETを積層することでSRAMの専有面積をビット当たり39%削減できることも報告し、横型および縦型GAAナノワイヤFETのプロセスフローも公開した(図3)。

横型がSOI(Silicon-on-Insulator)を用いているのに対して、縦型はバルク・シリコン基板を用いてこの表面にエピタキシャル成長をしている。また、横型がゲートラスト手法で、最初に形成したダミーゲートを最後にメタルゲートに置換しているのに対して、縦型はゲートファースト手法で、プロセス通りにゲートを初期段階で形成している。図3に示されたプロセスフローは略語だらけなので、それらを解読しつつ、FEOL(Front End of Line:トランジスタ形成工程)のプロセスフローを紹介しよう。

|

|

図3 横型GAAナノワイヤFET(中央左の写真および模式図)のプロセスフロー(左端)。縦型GAAナノワイヤFET(中央右の写真および模式図)のプロセスフロー(右端)。(a)横型GAAナノワイヤFET断面のTEM像、(b)縦型GAAナノワイヤFET断面のTEM像、(C)シリコン基板上にシリコン・ナノワイヤ・ピラーを形成した直後の上面SEM像 (出所:imec) |

横型GAA-NWFETプロセス

- まず、SOI基板のボックス層上にFin構造をパターニングする

- 次にダミーゲート(シリコン酸化膜)を堆積してから、イオン注入(I/I)を用いて無接合(JL)チャネルドーピングを行う。この際、ドーピングには、PMOSデバイスにはB(ボロン)を用い、 NMOSにはP(リン)を用いる。これらのイオンを活性化するため高速加熱アニール(RTA)を行う

- ダミー・アモルファス・シリコン(a-Si)膜を堆積したあと、CMP(ケミカル・メカニカル・ポリッシュ)で平たん化し、ゲート/パターニングを行う

- 次に、スぺ―サーを形成し、ソ―ス・ドレイン(S/D)領域を選択エピタキシャル成長(SEG)で形成し, イオン注入(I/I)で高濃度ドープ・ソースドレイン領域(HDD)を形成し、高速加熱アニール(RTA)を施す

- 以降、ダミーゲートをHigh-k/メタルゲートで置換するプロセスを行う。まず、コンタクトエッチ・ストップレイヤ(CESL)、層間絶縁膜(ILD)を堆積し、CMPで平たん化する。

- 次に、ダミーパターンを除去してから、High-k積層ゲート絶縁膜とメタルゲート(酸化ハフ二ウム膜(HfO2)+窒化チタン膜(TiN)+タングステン膜(W))を形成し、平坦化する

- 絶縁膜のビアを通してソースドレイン領域表面のシリサイド化を行う

- コンタクト・エッチ・ストップ層と層間絶縁膜を堆積し、コンタクト形成後、W(タングステン)を埋め込む

- BEOL(Back End of Line:多層配線工程)へ移行する

縦型GAA NWFETプロセス

- 低抵抗バルク・シリコン基板に不純物を含んだシリコンをエピタキシャル成長するーシリコンピラ―を形成する(図3の写真(C)参照)

- 底部となる絶縁層(SiO2ライナー/SiN)を形成する

- 以下、ゲートファースト(GF)工程を始める。まず、SiO2ライナーを除去してからオゾン酸化で清浄な層間SiO2膜を形成する

- ゲート積層膜(酸化ハフ二ウム膜(HfO2)+窒化チタン膜(TiN)+タングステン膜(W))をを堆積する

- WをCMPで平たん化し、メタルエッチバックを行う(Wエッチング - スピンオンCMPキャップ(SoC)層塗布形成 - SOC/W/TiNエッチング)

- SiO2ライナーを堆積し、ゲート電極を形成する

- 上部絶縁層(図3中の写真(C)左側の模式図の最上部に位置する紫色の部分)を形成する

- SiO2膜堆積後、CMP+希フッ酸およびSiconi(AMAT登録商標ドライケミカルプロセス)により軽くエッチングする

- 洗浄後、トップ電極(Ti/TiNライナー+W)を堆積する

- トップ電極をパターニングする

- 層間絶縁膜堆積後、コンタクトにW埋め込みを行う

- BEOL工程kへ移行する

将来はIoT向け低消費電力デバイスに応用計画

imecは、将来は、これらの縦型および横型GAAナノワイヤFETの特徴を生かして低消費電力ロジックデバイスやアナログ・RFデバイスへ応用していくという。いずれもIoTへのアプリケ―ションを想定している。

なお、この成果は。imecのコアCMOSプログラムのメンバー企業(GLOBALFOUNDRIES、Intel、Micron Technolohy、SK Hynix、Samsung Electronics、TSMC、Huawei、Qualcomm、ソニー)との協業により、プログラムの一環として実現したという。