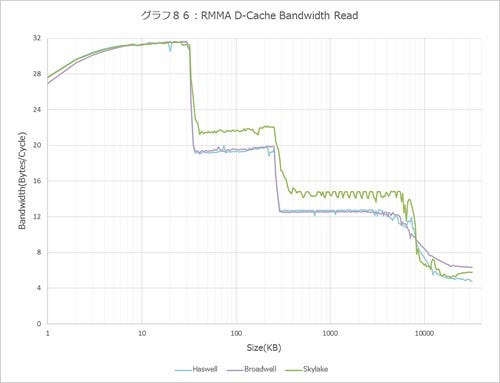

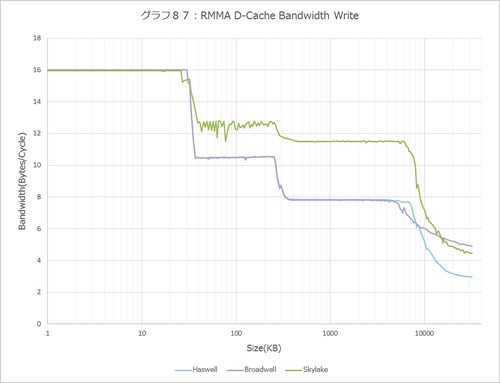

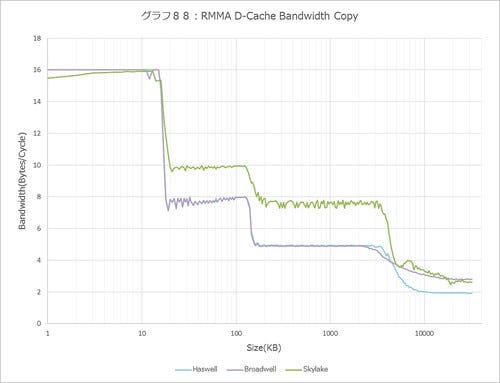

RightMark Memory Analyzer 3.8 - D-Cache(グラフ86~88)

さて、I-Cache/I-TLB周りはこのあたりにして、次はD-Cacheについて。まずグラフ86~88はRead/Write/CopyのBandwidth測定である。

L1に関してはRead 32Bytes/cycle・Write 16Bytes/cycleで、これはHaswell/Broadwellともに同じである。これはAVX命令を使ってフルに計算を行う際に必要な帯域なので、このこと自体は不思議ではない。さて、L2/L3であるが、グラフから

| L2 Read | L2 Write | L3 Read | L3 Write | |

| Haswell/Broadwell | 20Bytes/cycle | 10.5Bytes/cycle | 12.5Bytes/cycle | 5.0Bytes/cycle |

|---|---|---|---|---|

| Skylake | 22Bytes/cycle | 12.5Bytes/cycle | 15.0Bytes/cycle | 7.5Bytes/cycle |

といった数字が読み取れる。Copy(グラフ88)は当然これを反映した結果になっており、ラフに言ってSkylakeはHaswell/Broadwellと比較してL2で2Bytes/cycle、L3で2.5Bytes/cycleほど帯域が増していると結論付けられる。

この強化の理由の一つは、メモリがDDR3からDDR4になり、潜在的により高いメモリ帯域を利用できるようになっているから、それにあわせてL2/L3の転送速度も引き上げたということだろう。RMMTの結果で、1 Threadの時のRead/Writeの帯域がHaswell/Broadwellよりも引き上がっている理由はこのあたりにありそうだ。

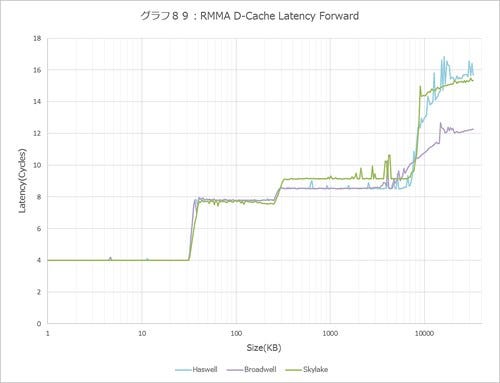

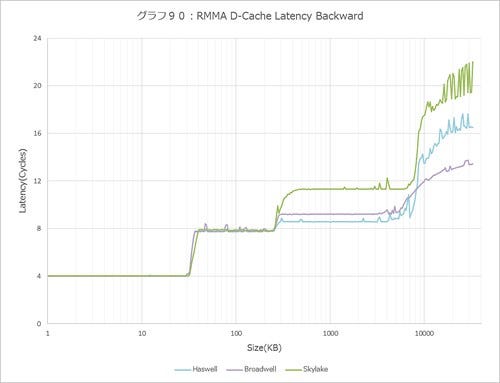

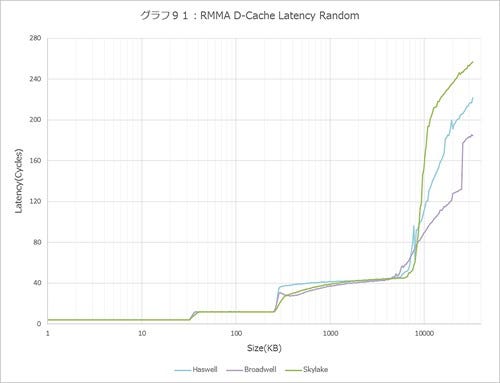

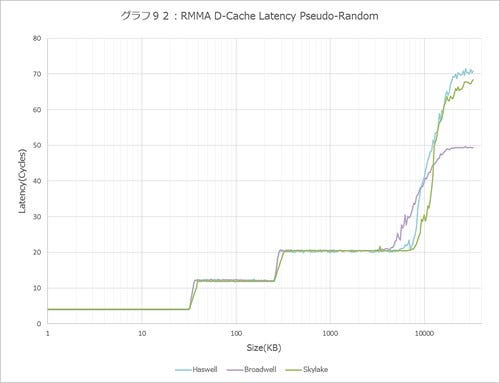

Latencyはどうか? ということでグラフ89~92がその結果である。さて、L1/L2に関しては、Forward/Backward/Random/Pseudo-Random無関係にHaswell/Broadwell/Skylakeが完全に一致しており、ここは同じままということだ。

実はこれはちょっと意外だった。BroadwellのCPU-ZとSkylakeの結果を比べていただくと分かるが、L2は従来8wayだった構成が4wayに変更になっており、ここで多少の差があるかと思われたからだ。

確かにL1 Missとなる32KB付近からの立ち上がりの角度が若干甘いといった違いはあるが、絶対的なLatencyそのものはほぼ8cycleと変わっておらず、(Hit率はともかく、Latencyの観点では)有意義な差があるとは言いがたい。

問題はその先のL3 Cacheである。SkylakeとHaswellは8MBの16Way構成、Broadwellは6MBの12way構成で、1wayあたり512KBという基本的な部分は一緒である。ただ、先に見た通り帯域を高めているのは明白なわけで、その分Latencyも減ったかと思えば、むしろ増える傾向にあった。

Forward(グラフ89)で1cycle、Backward(グラフ90)で3cycleほど増えており、帯域を高めた代わりに多少アクセスが遅くなっている。もっともPseudo-Random(グラフ92)ではほぼ同一として良いし、Random(グラフ91)ではピークのLatencyはほぼ変わらない(45cycle強)ながら、そこに至るまでのLatencyはBroadwellと同じ程度に低くなっており、単純にLatencyが増えている訳ではなく、内部の制御方式に若干の変更があると思われる。