DRAMとMRAMのハイブリッド動作が可能な「D-MRAM」

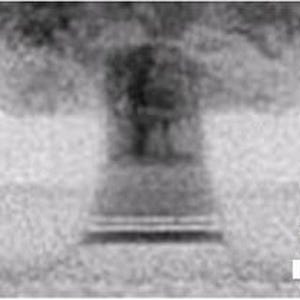

STT-MRAM(Spin Torque Transfer Magnetic RAM)はMagnetic Tunnel Junction(MTJ)に流す電流によって、その抵抗が高い状態と低い状態を取ることを使って状態を記憶する。この抵抗値はMTJの磁化の状態で記憶されるので、電源を切っても記憶は失われない不揮発性のメモリが作れる。

MTJを使ったメモリセルの基本的な構造はDRAMと同じ1MTJ-1T構造であるが、この構造はDRAMと同様に微小な信号を読み出すので、アクセス速度はあまり速くなく、高速アクセスを必要とするキャッシュには適しない。

次の図に示すように、高速のMRAMセルが各種提案されているが、どれもSRAMと同様に電源がオンの状態ではリーク電流が流れという回路になっている。

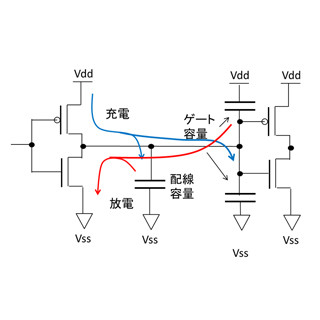

これらのMRAMセルをキャッシュメモリに使えば、電源を切っても情報は維持されるのであるが、電源をオフにすると、RAM部分の電源線の容量(実はセルを構成するトランジスタのゲート容量やドレイン容量)に溜まっていた電荷は(あるレベルまで)放電されてしまう。そして、電源をオンにする場合は、電源線の容量を元の電圧まで充電してやる必要がある。ということで、電源線の容量をCとすると電源オフ、オンだけでCV2のエネルギーが失われてしまう。

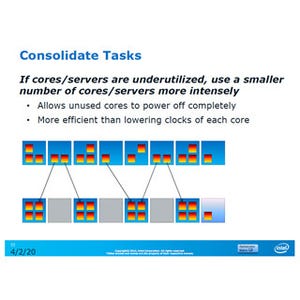

このため、東芝は、非動作時に電源を切るのではなく、メモリセルのリーク電流のパスを切り、パワーオフと同様にリーク電力を減らすというMRAM回路を考案した。この回路では、電源全体のオンオフを行わないので、電源線容量の充放電によるエネルギーロスは発生しない。また、メモリをアクセスしていない状態ではメモリセルのリーク電流は流れないので、パワーゲートしたのと同等の効果が短い時間粒度でも実現できることになる。

そして、このノーマリーオフ型のメモリセルを、短時間の状態記憶の場合はDRAMとして動作させ、長時間の記憶をする場合はMTJに記憶させるという動作をさせており、このメモリを東芝はD-MRAMと呼んでいる。

|

|

DRAMモードではMTJと直列のトランジスタをオフにしてハッチしたノードの容量の電荷で情報を記憶し、SAの前の左側のトランジスタを経由して情報を読み出す。MRAMモードではMTJに書き込みデータに応じた方向に電流を流して書き込み、読み出しはSAの前の右側のトランジスタを経由する |

DRAMモードでは、MTJと直列のトランジスタはオフとしてハッチされたノードの容量に溜まった電荷で情報を記憶する。そして、記憶ノードにゲートが接続されているトランジスタを通してデータを読み出す。このため、1C-1Tの通常のDRAMとは違い、読み出しを行っても記憶された電荷は無くならず、読み出しごとにリフレッシュする必要はない。

しかし、DRAMモードではリークにより記憶された電荷が減るので、記憶時間は10μs程度であるという。これより長い期間情報を記憶するには、DRAMと同様にデータを読み出して再書き込みを行うリフレッシュを行うか、次に述べるMRAMモードに切り替える必要がある。

MRAMモードでは、MTJに直列のトランジスタをオンにしてデータの1/0に応じた方向の電流を流して書き込みを行う。そして、MTJに流れる電流をセンスして読み出しを行う。

東芝が2012年のIEDMという学会に発表した論文によると、試作した1Mbitのアレイのシミュレーションでは、DRAMモードの書き込みアクセス時間は1.5nsであるのに対して、MRAMモードでは4.5nsとなっており、高速動作の観点から、まずはDRAMモードで記憶し、読み出しが継続して発生する場合は数回程度まではリフレッシュで情報を保持し、さらに読み出しアクセスが続く場合は、MARMモードに切り替え、MTJに書き込むという動作を行っている。

なお、このD-MRAMのキャッシュは各キャッシュラインに、そのラインがDRAMモードで動作しているのかMRAMモードで動作しているのかを示すフラグビットを持つ構成になっている。

また、従来の垂直磁化MTJにデータを書き込むには120μAの電流を25ns流す必要があったが、新型の垂直磁化構造とすることにより50μAの電流を3ns流すことで書き込みが行えるMTJを開発した。

高性能CPUのケースで評価してみると、CPUコア内のレジスタはスタンバイ状態で0.75nWの電力を消費しているが、動作と非動作の比率が1(50%の動作)であり、今回開発した垂直磁化MTJを使うD-MRAMセルを使っても120μs以上の非動作時間がないと消費電力は減少しない。

次の表に見られるように、L2キャッシュの平均的な非動作時間は30~100ns程度であり、書き込みエネルギーが小さくBETを10~20nsにできる新型の垂直磁化MTJを使うセルでなければ消費電力は減少しない。従来の垂直磁化MTJは書き込みエネルギーが大きいのでBETが1.9μsとなり、これをL2キャッシュに使用すると消費電力は増えてしまう。

この研究ではMTJの構造や材料を最適化して、より少ないエネルギーで書き込みを行える新型の垂直磁化MTJを開発した。