京都大学は9月10日、強磁性ナノ細線における磁壁移動のしきい値を低減する新しい方法を発見したと発表した。

成果は、同大化学研究所 小野輝男教授、小林研介 准教授(現大阪大学教授)、千葉大地准教授、Kab-Jin Kim研究員、小山知弘博士後期課程学生(現カイザースラウテルン工科大学研究員)、上田浩平博士後期課程学生、吉村瑶子博士後期課程学生、電気通信大学 仲谷栄伸教授、東北大学 水上成美准教授、大阪大学 河野浩准教授、NEC 深見俊輔氏、石綿延行氏、パリ南大学 Andre Thiaville教授、山田啓介氏、Jean-Pierre Jamet氏、Alexandra Mougin氏らによるもの。詳細は、英国科学誌「Nature Nanotechnology」に2012年9月10日付けでオンライン公開された。

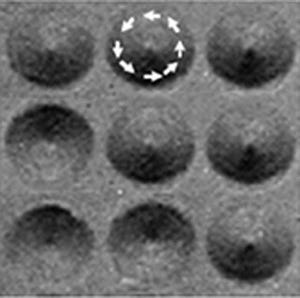

強磁性体の磁区と磁区の境界を磁壁と呼ぶ。磁壁はナノスケールの磁化のねじれ構造で、磁場だけでなくこれを電流によっても移動させることが可能であることを同大の研究グループが2004年に示している。

その後も、コバルトとニッケルを積層した強磁性薄膜において、磁壁を移動させるために最低限必要な電流(しきい電流)が、磁壁の構造変化を引き起こすために必要なエネルギーによって決まっていることが同グループにより明らかにされている。

|

|

|

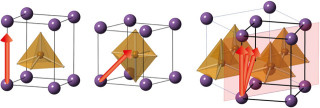

図2 磁壁の内部構造(ブロッホ磁壁とネール磁壁)の概念図。磁壁が電流で移動するとき、磁壁の内部構造はブロッホ→ネール→ブロッホ→…と周期的に変化する。しきい電流は両者のエネルギー差に依存する。このような磁壁の構造変化は、磁壁が外部磁場により移動する場合にも起こることが知られている |

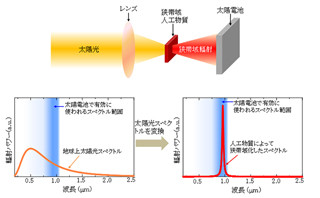

この現象を利用した新規メモリ素子が、IBMやNECにより提案されており、半導体メモリを凌駕する大容量性、高速性、低い消費電力を兼ね備えた廉価な不揮発性磁気メモリとして期待されている。これを実現するためには、しきい電流の低減が1つの大きな課題となっていた。

|

|

|

図3 IBM(左)とNEC(右)によって提案された電流による磁壁駆動を用いた不揮発性メモリの概念図。IBMの提案したメモリはレーストラック型メモリと呼ばれ、0と1の情報が書き込まれた磁性細線中の磁壁を電流で駆動して所望のデータを読み出す手法を用いる。NECにより提案されたメモリは中央の磁化方向を電流磁壁駆動によりスイッチさせデータを書き込む |

研究グループは、コバルトとニッケルを積層した強磁性薄膜を150nmの幅の細線に加工し、細線中の磁壁を電流で駆動する実験を室温で行うことで、しきい磁場(磁壁を動かすために必要な磁場)程度の大きさの外部磁場を印加することにより、磁場の方向によらずしきい電流がほぼ半減することを見出した。この結果は、しきい電流の起源である磁壁の構造変化(ウォーカーブレークダウン)が外部磁場によって誘起されたため、より低電流で磁壁が移動したと考えられるという。また、詳しい実験を行った結果、このような状況下における磁壁の移動速度が、電流および磁場による寄与の単純な足し合わせにより得られることが明らかにされた。

外部磁場によるウォーカーブレークダウンを利用したしきい電流の低減はこれまで報告例がなく、今回の成果はしきい電流の新しい低減方法を示しており、不揮発性磁気メモリの開発に大きな進展をもたらすと期待されると研究グループではコメント。また、磁壁移動速度の加算性を利用してスピン分極率およびダンピング定数といった材料定数を見積もることが可能なことも示されており、これらのスピントロニクスデバイス開発で重要となる量を決定する新たな方法を確立した点も成果とコメントしている。