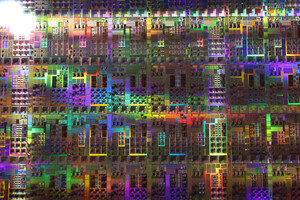

やや古い話になるが、2011年9月に財団法人 材料科学技術振興財団は2011年度の山﨑貞一賞受賞者を決定、11月18日に贈呈式を行った。すでに11回になるこの賞は、「材料」「半導体及び半導体装置」「計測評価」「バイオサイエンス・バイオテクノロジー」の4分野で創造的業績を挙げた方を対象とするものであるが、2011年は「半導体及び半導体装置」の部門で日立製作所 中央研究所エレクトロニクス研究センタ 主管研究員である久本 大氏が「フィン型MOSFETの提唱と実証」で受賞することになった。

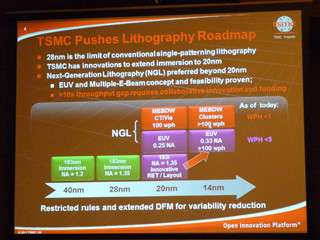

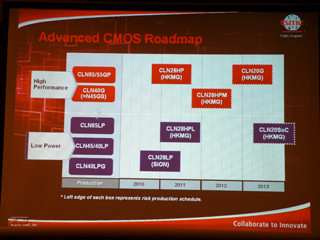

実は久本氏へのインタビューはこれが初めてではなく、2002年に一度行われているが、2011年はIntelがFinFETの構造を使ったTriGate Transistorの採用を明らかにしたり、TSMCがFinFETの採用をロードマップで明らかにするなど、いよいよFinFETの登場が現実のものとなりつつある。そうした事を踏まえて、改めてFinFETに絡めた話を久本氏にお伺いした。

Q:改めて、山﨑貞一賞受賞おめでとうございます。

ありがとうございます。

Q:一番初めにIEDMで発表されたのが1989年ですから、約20年。この手のものは、発表されてから実際に出てくるまで時間は掛かるものですが、それにしても結構時間かかった気がするのですが、いかがでしょう。

はい、やっぱりそう思います。ただ、最初から10年先、20年先を考えて研究しようという、そういうモチベーションで始めた研究ですので、そういう意味では仕方がない(笑)というところがあります。

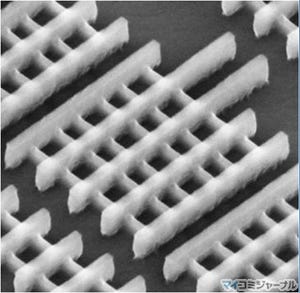

Q:業界としても、元々DELTAという名前で発表されたものが、FinFETという呼ばれ方となり、さまざま半導体ベンダが相次いでこれをそれぞれ独自の方法で、FinFETやTri-Gate、Ω-Gateだったりと色々な形で出して、にもかかわらず、実際にその製品化が形になったのが2011年に入ってからということで、結構遅かったな、という気がするのですが。

ええ、もちろん早く使っていただければその方が嬉しかったのは事実なんですが、ただ、事業部といいますか、実際製品を作る立場の目でデバイスの構造を考えて、どこの世代でMeetするのかというのを考えた時に、例えば最初に作った時は本当にFeasibility Checkというか物理的なチェックというイメージで作ってまして、その後にFinFETをやった時にも、25nmあたりをTargetと思ってやってましたので、そういう意味で言うと22nmで実用化されるというのは、ある意味リーズナブルな値という気はしてます。

Q:えーと、2007年に出された日立評論(*1)では、45nmでMeetするとか書いてありまして(笑)

そこで書いてる線というのは、丁度プレーナ型でやってるのと拮抗する点と言いますか、そういう意味ではそこでひっくり返すことができると。ただ実際に製品で使うことを考えた場合には、まったく同じ性能の物が2つあったら、決して新しいのは使わない訳です。リスクとかを考えなくてはいけないと言う事になりますので、そうしたリスクなどを含めても絶対勝てる所、そういったものを考えると、拮抗点はそこだと思うんですよ(笑)。

実際そういう絵を描いてみて、本当に実用化されるとしたら、その先だろうと思ってました。そういう意味では、まあまあ正しかったかな(笑)というような感じはありました。もちろん、早く使っていただければその方が嬉しかったんですけれど。

(*1):日立評論(注 リンク先はPDF)

Q:2000年に入って以降、さまざまなベンダがFinFET型トランジスタを相次いで発表をしましたよね? IBM、AMD、Intel、Infineon Technologiesなどがやっていたと思いますが。そういうベンダが、それぞれが独自の実装をしているのご覧になってどう思われました?

2002年くらいから一気に行ったっていう感じですね。本当の意味での製品化という事については、実際日立では残念ながら製品にもっていってませんのでそこの知識は無いんですが、ただ色々な開発段階での学会発表を見ていると、大体最初に我々がやった所の範疇に収まっているなあと、そういう感じがやっぱりありましたね。

Q:元々、3次元にするという閃きが、もちろん理屈としてプレーナ構造だとChannel Leakがどんどん増えて行って難しいという話はあるのですが、そこから3次元というのはなかなか常人では行かないと思うのですが。

それを最初やったのが1989年なんですが、80年代後半というのはSOIがかなり有力というか、SIMOXのウェハが開発されて、実際にデバイスを作って性能を調べられるという状態になりまして。例えば東芝の吉見さん(*2)などがたくさん論文を出されていて、色々なものがSOIで作ることができると言う報告が沢山出てくるようになっていました。そういうものを見ながら、CMOSの先の構造とかを色々考えてみた時に、やはりダブルゲート構造が一番いい構造だろうという風に考えるようになりました。

そこで、では実際にダブルゲートを作るにはどうやってやればいいんだろうという想いが、一番のきっかけとしてあります。ところが実際にプロセスでダブルゲート構造を作ろうとするとすると、一番よく知られているのはプレーナを積み重ねて、ゲート-チャネル-ゲートと積み重ねていく事になるんですが、そうなるとどうしてもSelf Alignのプロセスを作るという事ができない。この「縦に積み重ねる」というのが、プレーナ技術とまったく相性が悪い。それが一番の問題点という事に気づきました。

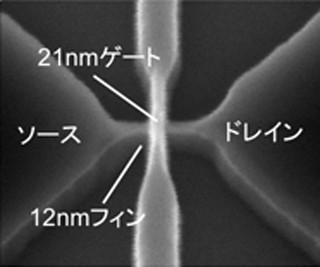

当時一番良くやられていたのは、例えばエピタキシャル技術を使って選択的にゲートの上に成長させるとか、そういう事をSOI上でいろいろ研究するというのが普通のアプローチだったかと思うんです。ところが私は、どちらかというと面倒くさいのは嫌だと(笑)。あと、例えば貼り合わせも結構難しそうだなと。現実的な問題として一番気にしたのは、「合わせ(精度)」ですね。例えばそういうプロセスを作ったとしても、「合わせ」が必要になると、Self Alignで作る事にならないという点が一番気になりました。ですので、何とかSelf Alignで作りたいと考えた時に、もうプレーナを積み重ねて作るって言うのはギブアップして、他の構造に行くしかないと。そう考えて、その中でFinを使えば何となく話が閉じる。Self Alignで行ける、と考えたのがまあ、縦にしたという理由になります。

(*2)吉見信氏(元 東芝研究開発センターULSI研究所。現在はSOITEC ASIA技師長)