スループット次第では14nmでもEUVをスルー

|

|

TSMC Vice President and Chief Technology Offficer,Research and DevelopmentのJack Sun氏 |

TSMCは11月28日、「TSMC Technology Symposium Japan 2011」を開催、併せて記者会見を実施し、同社Vice President and Chief Technology Offficer,Research and DevelopmentのJack Sun氏が20nmプロセス以降の同社の考え方を示した。

同社はすでに28nmプロセスの一部で量産を開始しており、2012年中には20nmプロセスのサービス提供を開始する計画。20nmプロセスでは従来のArF液浸リソグラフィに限界が来るということで、ダブルパターニングを採用する。ただし、それ以上のトリプル/クアッドパターニングなどについては、次々世代となる14nmプロセスでも「コストに見合わない」(同)との見方を示す。

|

|

TSMCの先端プロセスロードマップ。28nmプロセスでは初めてHKMGを採用したほか、第1世代のLow-R Cu配線材料を採用するなど、新しいプロセステクノロジーを多数採用したこともあり、提供するプロセスラインアップも多かったとのこと |

その一方で、NGL(Next Generation Lithography)としてMluti EB Direct Write(MEBDW)やEUVに投資を行ってきており、14nmプロセスでの適用などを目論んでいる。しかし、「現状でスループットはEUVで5WPH未満、MEBDWで1WPH未満」とのことで、量産ラインに求められるスループットを実現するには程遠いものとなっている。EUVのスループットが上がらない最大の要因は光源の出力がなかなか向上していないこと。EUVはArFまでのレンズを用いた露光機構ではなく、複数枚の鏡を用いた機構であり、反射するごとに出力が低下、最終的なウェハまで到達するまでに減衰が大きいことから、光源の出力向上が必須となっているが、いまだその問題の解決は見えていないという。

一方のMEBDWはさらにスループットが遅いが、これをクラスタ化することで、スループットの向上が見込めるとしており、「14nmはArF液浸のダブルパターニングを基本路線として、EUVが望むスループットを実現できないようであればスルーすることも考えている」という。

|

|

TSMCが考えるリソグラフィのロードマップ。NGLとしてEUVとMEBDWを検討して、すでにαツール機でウェハを製造したりといったことも行っているが、いかんせんスループットの壁が立ちはだかることになっている |

20nmプロセス以降ではプロセスの中身も大きく変更

すでに半導体はプロセスを単に微細化すれば低消費電力化され、性能が向上するというレベルを超えており、プロセスの微細化に合わせてさまざまな新技術の採用が求められるようになってきた。

20nm以降のプロセスで、その最たるものがFin-FETによるトランジスタの3D化であろう。すでに同社でも学会などでFin-FETを作れることは発表済みで、「14nm以降のプロセスで従来のプレーナ型と合わせて一般的なプロセスとして提供していく予定」とする。また、高移動度のチャネル材料の開発も進めており、すでにSi基板上での形成も達成しているという。

ちなみに同社の20nmプロセスはハイパフォーマンス向けの「CLN20G」と低消費電力向けの「CLN20SoC」の2種類を用意。28nmプロセスがLP/HPL/HPM/HPと多岐に渡ったことを考えると、1世代以前のシンプルなラインナップに戻ったようなイメージとなる。これについては、「28nmプロセスではHigh-K/メタルゲート(HKMG)のテスト的な意味などもあり、ラインアップが多くなった」とのことで、そうした新技術の筋を見極めた20nmプロセスでは提供ラインアップが少なくなったとしている。

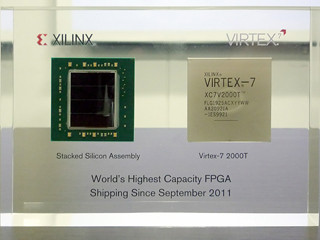

また、プロセスの微細化とは直接関係ないが、システムの高性能化という観点ではシリコンインタポーザとTSVを活用したダイ/チップの統合技術の開発も進めている。すでに2Dの統合技術としてはXilinxがTSMCと協力して同社のFPGA向けにSSIテクノロジとして同種の技術を活用しているが、こうしたシリコンインタポーザ上に複数のダイを集積して、配線密度の向上などによる高性能化といったバックエンドのサービスを2012年から開始する計画だという。

さらに3D化。つまり、ロジックの上にほかのロジックやメモリなどを搭載する技術についても現在開発を進めており、「TSVにかかるストレスが下部のトランジスタ層にどの程度影響を与えるか、そこで発生する熱の拡散をどうするか、デザインインフラをどう用意するか、アセンブリテストはどうするのか、などの課題がまだ残されている」とさまざまな問題が残っているとするも、2014年ころにはサービスとして提供していければとの見方を示している。

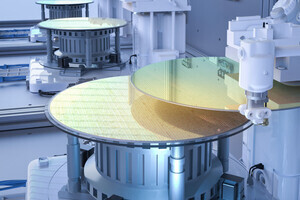

なお、同社では450mmウェハに対する取り組みも進めており、パイロットラインを2013~14年にかけて構築し、2015~2016年をめどに20nmプロセスで量産ラインを構築する計画であるとしている。