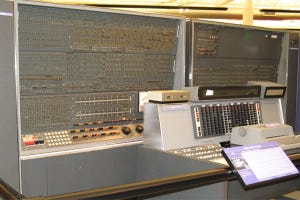

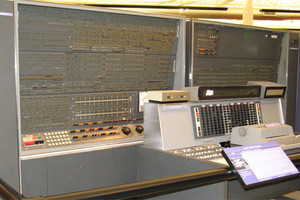

CDC6600のアーキテクチャ

アーキテクチャ的には、CDC6600はCPUと周辺装置を制御する10台のPPUからなるヘテロマルチプロセサのシステムである。CPUは1語60bitで、レジスタは整数と浮動小数点数で共用されていた。CDCは1文字を6bitで表わしており、PPUは2文字を格納できる12bit語のプロセサであった。

PPUは物理的には1台のプロセサであり、今でいう、マルチスレッドプロセサで10個のスレッドをサイクルごとに切り替えて実行するプロセサになっている。

-

図1.23 CDC6600のハイレベルブロック図。CentralプロセサとPeripheralプロセサがCentralストレージを共有している。そして,Centralストレージには拡張コアストレージが付けられるようになっている

また、リファレンスマニュアルには次の図が載っている。右側のCPUは24個のレジスタを持ち、Add、Multiply2個、Divide、Long add、Shift、Boolean、Increment2個、Branchの各実行ユニットにつながっている。左側はPPUで、時分割で10個のプロセサが存在するように動作する。周辺装置を接続するIOチャネルは12あり、PPUとIOチャネルの対応はチャネルスイッチで切り替えられるようになっている。

なお、現代では、割り込みを使ってどの装置にサービスが必要かを判別し、1つのプロセサで複数のIO装置の面倒を見るというやり方が一般的であるが、当時は、割り込みの使用は一般的ではなく、1つの装置を1つのプロセサが制御するというやり方が一般的であった。

しかし、IO装置の数だけペリフェラルプロセサを用意するのはもったいないので、CDC6600では時分割で処理するスレッドを切り替えて、1つのCPUハードウェアで10個のペリフェラルプロセサを実現している。

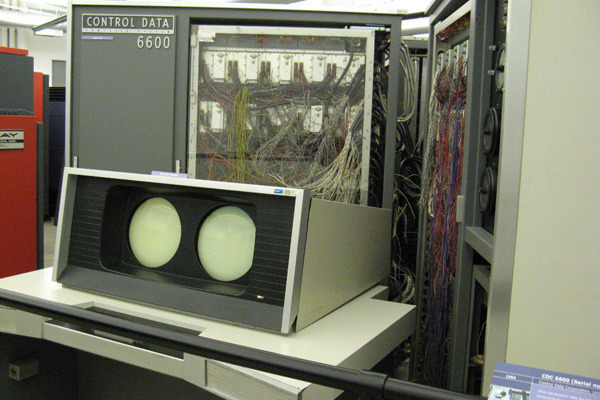

キャビネットの図1.20に書かれているように、4本の十字の腕に、それぞれ4枚のシャシーが収容されており、内訳は、

- 1. PPU

- 2. CPU Divide

- 3. 16K Store

- 4. 16K Store

- 5. CPU Control

- 6. CPU Multiply

- 7. CPU Registers

- 8. CPU Add Shift

- 9. 16K Store

- 10. 16K Store

- 11. 未使用

- 12. 周辺(IOチャネル)

- 13~16. 16K Store

となっている。

図1.24に見られるように、CPUのファンクショナルユニットは、FADD、FMUL(2)、FDIV、Add、Inc(2)、Boolean、Shift、Branch と全体では10個のファンクショナルユニットがある。命令実行ユニットはスコアボードを持ち、命令は、入力オペランドが揃い、使用するファンクショナルユニットがビジーでなく、結果を格納するレジスタが確保できる場合には、命令の実行が行われるようになっており、通常、少なくとも2~3個のファンクションユニットが並列に動作する状態を維持できるという。

なお、CDC 6600はスコアボードを使った最初のプロセサである。このスコアボードによる命令のOut-of-Order実行は、後の命令の実行完了が前の命令の実行完了より先になる場合があり、割り込みが起こった場合の状態は順次実行では起こらない状態になることがある。つまり、いわゆる、Precise Interruptにはなっていない。しかし、CDC 6600では割り込みを使っていないので、これは問題にならなかったと思われる。

システムクロックのメジャーサイクルは1μsで、メモリのアクセスはこのサイクルになっている。マイナーサイクルは100nsで、CPUのパイプラインは、100ns(10MHzクロック)で動作する。CPUは毎サイクル1命令を発行できるので、最大では10MFlopsの演算を行う事ができるが、平均的には3MFlops程度というところであった。

構造の中で面白いのはStunt Boxというブロックがある点である。Stunt Boxは内部にメモリアクセス要求を保持する4つのレジスタを持ち、メモリアクセスの効率を高めるユニットである。

通常のメモリアクセスはM1レジスタに入れられ、バンクがビジーで無ければ要求は受け付けられてアドレスバスに送り出される。しかし、バンクがビジーで、その時に発行できなかったリクエストはM4、M3、M2からM1と送られる。この間の後続のメモリアクセス要求は、バンクがビジーで無ければ受け付けてメモリアクセスを開始することができる。

即時に発行できなかったリクエストは、M4、M3を経由してM2にリクエストが来ると、外部からのリクエストは待たされ、M2のリクエストをM1に入れて優先処理する。転送は75nsサイクルで、最大300nsで4バンクにメモリアクセスを出せるようになっていた。

なお、Priority回路で、同一バンクへのReadとStoreが同時にStunt Boxに入らないように制御して、メモリアクセスオーダが逆転するのを防止している。

CDC 6600のメモリやデータレジスタは60bit長で、命令は15bitのものと30bitのものがあった。そして、演算命令は3アドレス命令で、オペランドはすべてレジスタを使うという形式の命令になっており、CPUが実行する命令は演算命令を中心とした簡単な命令に限定されていた。これは、RISCの命令の考え方であり、CDC 6600はRISCの元祖とも言われる。Seymour Crayは速度至上主義で、速度が低下するメモリ管理ハードウェアを付けることを認めなかった。多分、メモリオペランドのサポートも性能を低下させるハードウェアと考えていたのであろう。

なお、CDC 6600は、図1.26に示すように、ECSメモリのコントローラを経由して4台のシステムを結合して4CPU構成まで拡張できるようになっていた。

CDCは6600に続いて、廉価版の6400、6500を開発した。6400は、演算ユニットの並列動作を行わず、命令を順番に実行するマシンであった。

また、図1.26のように最大4台の6600 CPUを接続した構成も考えられていたが、実際に商品化されたのは6600タイプのCPUと6400/6500タイプのCPUを持つ2CPU の6700というマシンだけであった。

(次回は4月6日に掲載します)