低性能デバイスへの2D材料の導入

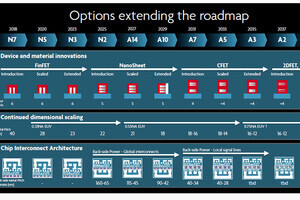

大手半導体メーカーや大学グループが最先端のCFETアーキテクチャの伝導チャネルに2D材料を導入するためのソリューションを模索している一方で、imecは多くの集積の課題と予想されるコストを考慮して、別の方向に向かうことにした。

2D材料の導入にかかる労力と予想コストを削減するため、imecでは2D材料をあまり先進的ではないノードや性能の低いデバイスに段階的に導入することを選択した。その結果、モジュール開発と300mmウェハプロセス開発を平面2Dデバイスに集中させ始めている。非常に複雑なCFETアーキテクチャに2D材料を統合する必要が生ずるころには、これまでに学んだことを活用できるようになるだろう。imec内部では、2D材料はすでに300mmファブに導入されており、誘電体堆積とソース/ドレイン コンタクト形成のソリューションは準備が整い、信頼性を向上させる方法が模索されている。

2D材料採用のA7技術ノードのプレーナーnおよびpチャネルFET

imecは、2D MX2ベースのデバイスを、imecロジックテクノロジロードマップのA7ノード(いわゆる7オングストロームあるいは0.7nm)に最初に導入することに取り組んでいる。

将来のテクノロジ世代では、Siチャネルを備えたCFETが高性能ロジックCMOSを構成し、電力はBSPDNによってこれらのロジックデバイスにルーティングされ、最終レベルのキャッシュメモリは高度な3D統合テクノロジによってロジックCMOSに接続される可能性がある。プレーナ2D MX2ベースのデバイスが適用されるのは、バックエンド・オブ・ライン(BEOL)またはウェハの裏側にある周辺デバイスとしてであろう。低ドロップアウト電圧レギュレータ(LDO)と、ロジックCMOSデバイスのブロックをオン(およびオフ)する低性能電源スイッチへの適用について考えてみることにしよう。

imecの研究者によるシミュレーションでは、MX2チャネルを備えた平面nMOSデバイスがこのようなアプリケーションに非常に有望であることが示されている。ウェハの裏面またはBEOLでは、それらを実装するために利用できるスペースがより多く存在する。そのため、それらのフットプリントは前面と比較して緩和され、より大きな平面デバイスアーキテクチャ(n型またはp型)を採用できる。

これらのアプリケーションでは、レイヤートランスファーが推奨される堆積技術となる。BEOLと裏面処理はどちらも、前面にすでに存在するデバイスのパフォーマンスを低下させないように、利用可能な温度バジェットを400℃未満に制限している。このような低温で(産業的に互換性のある方法で)2D材料を直接成長させることは、品質の悪いレイヤーを生成する可能性があるため困難である。

A3ノードの平面2DベースのnおよびpFET

並行して、imecではA3(いわゆる3オングストローム、もしくは0.3nm)テクノロジノードに2D材料を導入するための開発が進行中である。

ここでimecはCMOS 2.0への段階的な移行を見込んでいる。これは、コンピューティング・システム・オン・チップ(SoC)11)内にハイブリッド集積を持ち込むことでムーアの法則の潜在能力を解き放つことができるパラダイムチェンジである。これは、SoCを(STCOの助けを借りて)異なる機能層に再分割し、高度な3D相互接続とバックサイド技術を使用してそれらを再接続することによって実現される。SoCの各機能部分に最先端のノードを使用する代わりに、機能層は、その制約に最も一致する技術オプションを使用して構築できる。極端なデバイス密度を必要とする層(高密度ロジックなど)は、最もスケーリングされた技術(つまりCFET)で構成される。

CMOS 2.0により、SoCのさまざまなレイヤーに2D材料をスムーズに導入できる。例えば、ウェハの裏面にあるアクティブ相互接続の一部としての電源スイッチ、またはメモリレイヤーの一部としてのプレーナMX2デバイスなどである。

imecでは、このようにプレーナーデバイスへの2D材料を採用する検討に加えて、GAAナノシートトランジスタの伝導チャネルとして2D材料を導入する研究も行っている。

2DベースのGAAナノシートとCFET

2D材料のプレーナーデバイスへの適用検討が300mmウェハ対応のクリーンルーム内で行われている一方で、imecはGAAナノシートトランジスタの伝導チャネルとして2D材料を導入する研究も同時に行っている。

これらの研究はラボ規模で行われているが、製造工場と互換性のあるツールとプロセスを使用している。これらの研究の目的は、長期的にはCFETに関連するナノシート固有のモジュールに対する2D材料の統合の影響に対処することである。

次回はナノシートチャネルのリリース(つまり、ナノシートチャネルを形成するための犠牲層の除去)、内部スペーサーの形成、および置換金属ゲートの統合ステップについて考えてみたい。

本記事はimecの技術解説記事「Introducing 2D-material based devices in the logic scaling roadmap」をimecの許可のもと、翻訳・改編したものとなります

参考文献

[11]“CMOS 2.0: bringing heterogeneity inside the system-on-chip”、imec

César Javier Lockhart De La Rosa(セザール・ハビエル・ロックハート・デ・ラ・ロサ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)