ジャパンディスプレイ(JDI)と、台湾のLEDディスプレイ開発企業である方略電子(PanelSemi、パネルセミ)は、共同開発する半導体パッケージ技術の詳細を明らかにした。GPUやHBMを組み込んだ大型チップの剛性を高めつつ薄くするために、樹脂材料をセラミックに置き換える。また生産性の向上もめざし、大型ガラス基板をキャリアに用いる。量産はJDI石川工場で行う。

生成AIの急進を反映して、AIチップの需要は急速に拡大している。膨大なデータを扱う学習や推論をこなすために実装する、GPUやHBM(High Bandwidth Memory)は大型化が進み、NVIDIA「GB200」のチップサイズは85×76mmにもなった。これにつかうHBMなどを載せるインターポーザー(中継基板)サイズは58×56mmである。

これだけの大きさになると、異種材料(シリコンと樹脂基板)の熱膨張係数(CTE)差から反りが生まれ、信頼性や歩留まりの低下につながる。そこでJDIと方略電子は解決策として、マザーボード上のビルドアップ基板のコア材として広く使われている化学大手の高機能樹脂を、セラミックに変更した。これでCTEは11~14PPM/Cから6~12PPM/Cへと、シリコンにより近くなり、反りにくくなる。

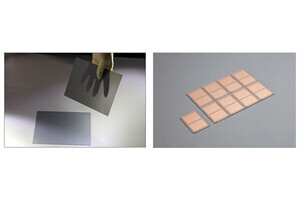

セラミックコア基板は150mm角で厚さは0.3mmだ。方略電子は2024年、日本ガイシと提携してセラミックをつかった半導体向けの高機能プリント配線板開発を進めることを明らかにしている。

ビルドアップコア材の変更に加え、ビルドアップ基板とインターポーザーを一体化した構造「IIS」(インターポーザー・インテグレーテド・サブストレート)を提案。これによって剛性を高め、厚さもユーザーの要望によっては約1mmへと薄化できるようになる。

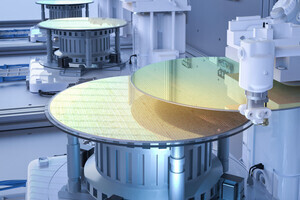

今回開発した基板の生産は、スマホ向け液晶パネルを量産していた石川工場で行う。TFT(薄膜トランジスタ)量産設備は半導体基板製造に生かせるが、回路形成を行う銅配線設備は新たに導入する必要がある。一連の設備をそろえた後、両者は「できるだけ早く量産に入りたい」としている。

なお量産にあたり、パネルセミはフラットパネルディスプレイ(FPD)パネル技術を流用して生産性を高める。インターポーザーのサイズは150mm角だが、これを半導体ガラス基板(515×510、600×600mm)上にスキマなく並べて一気に処理。ガラスからの剥離はサーマル方式で行う。ガラス基板をキャリアにつかう方式はラピダスも採用するなど、拡大傾向にある。