Ansysの日本法人であるアンシス・ジャパンは12月12日、「SEMICON Japan 2024」の開催に合わせる形で複雑化する先端半導体設計の分野でどのようにシミュレーション技術が活用されているのかに関する説明会を開催。TSMCやNVIDIAといった先端プロセスを活用する企業らと協力して、さまざまな課題解決に挑んていることを紹介した。

進む半導体設計におけるAIとシミュレーションの連携

AysysはNVIDIAとソリューションの相互活用で長年にわたって連携してきた関係だが、11月19日付でそうした関係性をさらに強化することを目的に、NVIDIAのAIフレームワーク「Modulus」をAnsysのクラウド最適化ビッグデータ解析プラットフォーム「SeaScape」に統合することを発表した。

この統合の取り組みは大きく2段階に分けることができる。まず1段階目としてはModulasにて、3Dのシミュレーションデータを作成し、それをAIに学習させる。2段階目は、そうして学習させたデータをもとに、CAEを置き換えることができるAIサロゲートモデルを作成するというもの。さらに、この相互のやり取りを繰り返すことでサロゲートモデルの精度を向上。その結果、シミュレーションモデルと変わらない精度ながら、より高速に結果を得ることが可能となる。

Ansysでは、半導体設計向けに、パワーインテグリティおよび信頼性サインオフプラットフォームとして「Ansys RedHawk-SC」、「Ansys Totem-SC」、「Ansys PathFinder-SC」、「Ansys RedHawk-SC Electrothermal」を含むマルチフィジックスシミュレーションエンジンを提供しているが、Modulusの物理情報AI技術は、それらのシミュレーションを補完する存在となり、この活用により、GPUやHPC、AI、スマートフォンをはじめとする先端プロセスを用いたロジックや高度なアナログICなどの製品設計の容易化、設計期間の短縮などを図ることができるようになるという。

AnsysのDirector、Asia Semiconductor Salesを務めるBill Baker(ビル・ベイカー)氏は、「例えば3D ICの場合、ダイの積層などで熱が問題になる。そのため、設計段階で発生する熱がどの程度になるのかといったことを予測しておく必要がある。それをSeaScapeをベースとした素材や物理、機械特性などを変更させた複数のパワーパターンをModulasというAIフレームワークに学習させることで、各種の3Dソルバに基づくシミュレーションとほぼ同精度の予測を機械学習(ML)でできるようになる。我々の行ったテストでは、熱に関するシミュレーション結果とMLに基づく結果の相対的な誤差は0.1%未満で、処理速度は実行サイズによるが、272倍~1310倍高速化されることを確認した。あくまで熱に関する予測の結果だが、3D ICの設計に重要な要素の予測をAIを用いることで、これまで以上に高速に高い精度で出せることが示された」と、その取り組みの成果を強調する。

電気と光の1パッケージへの統合にシミュレーションを活用

NVIDIAとのAIとシミュレーションの連携のほか、TSMCともAnsysはさまざまな協力を行ってきている。中でも最新の取り組みは、単なるロジック半導体の設計ツールの1つとしてではなく、TSMCの「Compact Universal Photonic Engines(COUPE)」に向けたマルチフィジックスソフトウェアでの協力関係の構築となる。

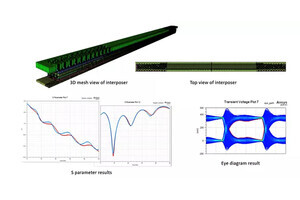

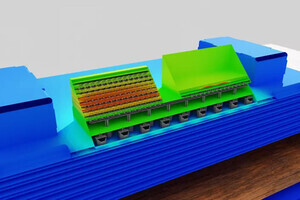

COUPEは、Synopsysの3DIC Compilerプラットフォームと統合されたAnsysのマルチフィジックスソリューションを活用することで、光ファイバーとチップの結合、電子光統合チップ設計、パワーインテグリティ検証、高周波電磁界解析、重要な熱管理など、シリコンフォトニクスに求められるさまざまな要件を踏まえた設計を可能とするもので、これにより複数の電気ICとフォトニックICおよび光ファイバー接続を1パッケージ(Co-Packaged Optics:CPO)に統合することができるようになる。

Ansysのソリューションとしては、光入出力シミュレーション向け「Ansys Zemax」、フォトニックシミュレーション向け「Ansys Lumerical」、マルチダイパワーインテグリティサインオフ向け「Ansys RedHawk-SC」ならびに「Ansys Totem」、ダイ間の高周波電磁界解析をモデル化する「Ansys RaptorX」、マルチダイヘテロジニアスシステムの重要な熱管理向け「Ansys RedHawk-SC Electrothermal」が含まれている。

中でもLumericalについては、TSMCのModeling Interface(TMI)とシームレスに動作し、TSMCのProcess Design Kit(PDK)と共同設計された、電子光回路シミュレーション向けカスタムVerilog-Aモデルの提供も行われているほか、TSMCとAnsysにMicrosoftを加えた3社の協業として、MicrosoftのAI開発総合プラットフォーム「Azure AI」上で動作するNVIDIAのAI向けGPUを搭載した「Microsoft Azure NC A100v4シリーズ仮想マシン」を介して、Lumerical FDTDフォトニクスシミュレーションを従来比で10倍以上高速化することに成功したことも発表している。

シリコンフォトニック集積回路(PIC)を統合した形の3D ICの場合、パッケージ上にPIC、HBMなどの高性能メモリ、高速演算ロジックICなどが搭載されることとなる。この場合、チップレベルからシステムレベルまでのサイズの異なる各レイヤに対して、光、電気、熱、機械などのそれぞれの特性を踏まえる必要があるが、それを連動して考える必要があり、計算量は膨大になり、結果として演算時間も長くなる傾向にある。この計算時間が短縮されれば、半導体そのものの設計期間を短縮できるようになり、市場投入までの時間も短くすることができるようになる。

同社は現在、Synopsysが買収に向けた手続きを進めているが、CPO向けマルチフィジクスソリューションとしては、そうしたSynopsysとはFusionコンパイラをはじめとしたデジタル部分の設計で連携している一方、Synopsysの競合であるCadence Design Systemsともアナログ(RFやフォトニクス設計)部分の設計で連携を進めており、EDAツールとシミュレーションのつながりを深めているという。

-

CPOの実現にはデジタル(ロジック)の半導体設計のみならず、アナログ(RFやフォトニクス)の半導体設計を融合させる必要があり、それぞれで生じる物理特性などを加味したシミュレーションを実行し、実際に製品を製造する前の課題の洗い出しなどを行う必要がある

なお、こうしたCOUPE向けデザインソリューションの共同設計については、TSMCが推進するオープンイノベーションに合致するものとして、10月に開催された「TSMC 2024 Open Innovation Platform(OIP) Partner of the Year」のアワードとして4件の取り組みが表彰されたほか、14件のAnsysが関わった論文も発表され、そのうち3つがCOUPEにフォーカスしたものであったという(2件がAnsys独自のもの、残る1件がSynopsysとの共著)。