AMDのGen 4 EPYCの詳細について先ごろ紹介させていただいたが、それに続き、今回は「Instinct MI300AおよびMI300X」の話をご紹介したい。

といっても、実は今回AMDはMI300AやMI300Xのスペックを一切公開していない。動作周波数や内部の演算器の構成などは依然としてまだ藪の中であり、当然性能そのもの(と消費電力)についてもまだ不明なままである。

では何が公開されたか? というと、MI300A/MI300Xのパッケージ構造である。

まず基本的なところから。Instinct MI300Aは2022年のFinancial Analyst Dayの折にMI 300として発表されたもので、NVIDIAのGrace Hopperと同じようにCPUとGPUを1つのパッケージに収めたAPU構造である。

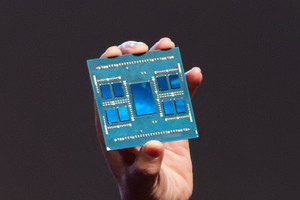

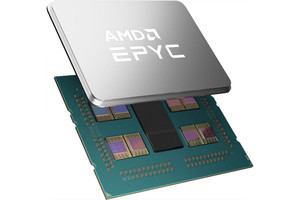

今回はもう少し詳細が明らかにされており、HBM3が128GB(16GB×8 Stack)構成になっていることが示された(Photo01)。これに加えて公開されたのがMI300Xである(Photo02)。こちらはMI300XのCPUを取り去り、その代わりにGPUを搭載したものとなる。

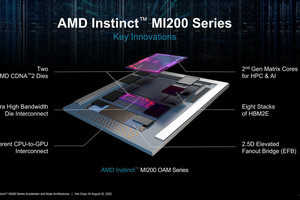

さて、問題はこれのパッケージ技術である。実際のチップはこちら(Photo03)で示すように、割とPhoto02と近い構造になっている訳だが、AMDによるCG(Photo04)もこれと同じような構図になっている。

ここでチップの図を改めて示してみると、図1の様になっていると考えられる。

で、このオレンジの枠は何だろう? という話になる。てっきりこれはHBM3のI/Fで、これが6nmで製造されているのかな? と思ったのだが、Sam Naffziger氏(SVP, Corporate Fellow and Product Technology Architect)に確認したら全然違っていた。そもそもこのオレンジ色のものは「なんでもない」との事。3D V-Cacheを搭載したZen 4コアは、3D V-Cacheの周囲を高さを揃えるためのサポーターが囲っている(Photo05)が、これと同じ役割を果たすらしい。要するに単に高さを揃えるためのもので、機械的にはともかく、内部構成には一切関係のないものだそうだ。

ではどういう構造なのか? なのだが、図2の様になっているのだそうだ。

つまり4枚のIoDがまず配され、このIoDの上に2つずつGPUのダイが3D Stackingの形で載る。HBMのI/FはIoDの方に搭載されており、IoD同士あるいはIoDとHBMはSilicon Interposerで接続されるという形だ。AMDはMI300Xを12個、MI300Aを13個のChipletで構成していると説明したが、このChipletにはSilicon Interposerの分は含まれない事になる。つまりGPU×8+IoD×4で12個、という訳だ。このSilicon Interposerであるが、全体を覆う形ではなく部分的に接続されるものになると考えられる。理由は簡単で、MI300A/X全体を覆えるような巨大なSilicon Interposerは製造できないからだ。いや厳密に言えば製造そのものは可能だが、これをやるとHBMの接続ができなくなる。これについてはすでにAMDはInstinct MI250でEFB(Elevated Fanout Bridge)という技法で実装を行っており、今回もこれを採用したものと思われる(Photo06,07)。

一方でChipletとGPUの接続は、3D V-Cacheと同じくTSMCのSoICを採用しているものと思われる。

さて、ここまではMI300Xの話をしてきたが、ではMI300Aは? というと、図3の様になる。

ここで右下のIoDに搭載されるCPUのダイはGenoaのものそのもの(“Exact same”)だそうである。ダイの再利用も極まれりである。

ちなみにこのIoDはTSMCのN6で製造され、機能として

- CPUないしGPU Dieの接続

- Infinity Cache

- Infinity Fabric(とひょっとしてPCIe?)のI/F

- HBM3のI/F

を持つことになる。

元々Infinity FabricはOut-of-Boxの接続には向いておらず、チップ内のFunctional Block同士~In-Boxの接続までに使われる構成である。

今回はまだ詳細が明らかになっていないが、恐らく図2で1つのIoDダイの上に載る2つのGPUダイ同士も、4つのIoDダイ同士もInfinityFabricで接続されており、さらにMI300A/300X同士もInfinityFabricでの接続となる(Photo08,09)。

-

Photo08:この例では4つのMI300Aが接続されるケースで、これで1ノードを構成。ノード同士の接続は「それこそEthernetでもInfiniBandでもSlingShotでも」との事だった。多分El CapitanだとSlingShotになるだろう

-

Photo09:8つのMI300Xが搭載されたモジュール。各々はOCP(Open Compute Project)のOAM(OCP Accelerator Module)に準拠するとの事。なので「という事は消費電力は最大700W?」と確認したら笑って誤魔化された

ところで最後に性能についての推定を少しご紹介したい。最初に書いたように性能に関しては一切公開されておらず、唯一示されたのがMI300Xだと400億個のパラメータをIn-Memoryで格納できるという話である(Photo10)。

まぁこれはメモリ容量をそのまま当てはめただけであるが、例えばGPT-3の175BのパラメータをMI300Xだと5つで格納しきる、というのはそれなりにインパクトがあると言えばあるのだろう。

それはさておき、今年のCES 2023の基調講演で、MI300はAI性能がMI250の8倍、性能/消費電力比が5倍になると説明されている。

これは恐らくMI300Xを指しての事と思われる。MI250の構成は以前こちらでご紹介した通りだが、ラフに考えると1つのチップの上に載るダイの数が4倍(2つ→8つ)、そしてMI250XがAI向けだとFP16/BF16までのサポートだったのに対し、MI300XではFP8のサポートがある(つまりこれで2倍)と考えると、実はこれで8倍という計算になってしまう。ただMI250Xの内部構造を見ると、ダイあたり4×14×2で112個のShader Engineが搭載されている(ただしうち2つは未使用)。つまりパッケージ全体では110×2=220個である。これに対しMI300XではPhoto04を見るとダイあたり4×10で40個、これが8つで320個のShader Engineにしかならない。もっともこれRDNA 3みたいに、Shader Engineあたりの性能が倍増している可能性もあり、そうだとするとMI250X換算で言えば640個のShader Engine相当ということになる。

つまりShader Engineの数では2.9倍ほど。これにFP8のサポートを加味して性能は5.82倍程度。8倍とのギャップをどう埋めるか? というと、動作周波数を1.375倍に引き上げれば辻褄が合う。MI250XはBoostで1.7GHz動作であり、これを2.34GHz程度まで引き上げられれば、丁度8倍になる計算だ。そして仮にこの2.34GHz動作の場合の消費電力が700W(OAMの48V供給時の最大消費電力:12V供給だと600W)になったと仮定すると、MI250Xが最大560Wだから1.25倍に消費電力が増える。性能8倍、消費電力1.25倍だとすると性能/消費電力比は6.4倍なので、ちょっとまだ辻褄が合わない。実際には900W近い、とすると大体性能/消費電力比が5倍に収まる計算である。2.34GHz動作、と考えるとこの900W(OAMの仕様はもちろんぶっちぎっている)あたりが現実的な数字になりそうな気がする。

さて、ここまではMI300Xの話であるが、MI300Aは? というと、GPUは6ダイだからピーク性能はMI300Xの4分の3(その分消費電力も4分の3)、CPUの方はGenoaベースのEPYC 9654が12ダイで360Wだから、3ダイなら90Wと仮定すると、合計765Wという計算になる。ただFrontier同様に性能/消費電力比を引き上げるために、多少動作周波数を下げて消費電力を落としているのではないかという気もする。

GPUは2GHz、CPUも3.5GHz程度まで落とせば、全体として700W程度まで消費電力を下げるのは難しくないだろう。その場合、GPU部分の性能はMI250Xの5.14倍という計算になるが、これはAI(つまりFP8のMatrix演算)の場合の話で、FP32/FP64 Vectorに関してはこの半分の2.56倍かその程度に落ち着くものと思われる。MI250XのFP64の性能がピークで47.9TFlopsとされるから、122.6TFlops程度ということだろうか?

ちなみにEl Capitanのノード構成はぼちぼち資料が出て来ているのだが(Photo11)、これを読むとCompute Nodeは4つのGPU+1つのCPUの組を2セットまとめて、これで1枚のブレードになるらしい。

このGPUが全部MI300Aだとすると、ブレード1枚あたりの性能はFP64で980TFlops程度。CPUも全部フルに使ったとして1000TFlops(=1PFlops)といったところか。2EFlopsを実現するには、ブレードが2000枚あれば済む計算になる。ノード数で言えば4000ノード程度で、ほぼ1万ノード近いFrontierから半減している計算になる。

この計算がどこまで合っているのか、は今年11月のTOP500の結果を見ないと判らないところだ。とりあえずMI300Aはすでにサンプル出荷中、MI300Xは今年第3四半期中にサンプル出荷開始とされる(Photo12)。