今年もHot Chips 34が無事開催した。初日はTutorialということで午前中はCLX、午後はMLIRが取り上げられた。こちらはこちらでまた説明の機会がありそうだが、今回はこれはスルーして、2日目というかConference 1日目である。午前中は“GPUs & HPC”ということで

- NVIDIA Hopper

- AMD Instinct MI200 Series

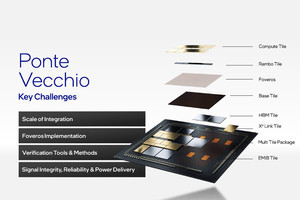

- Intel Ponte Vecchio

- Biren BR100 GPGPU

の4つの発表が行われた。

このうちInstinct MI200 SeriesとPonte Vecchioの2つについて説明したい。

AMD Instinct MI200 Series

AMD Instinct MI200 Seriesの詳細は昨年11月のAMD Accelerated Data Center Premiereイベントで発表されており、その詳細も公開されている。これらの情報と重複する部分もあるが、今回新発表の情報もあったので、復習も兼ねてこのあたりをまとめてご紹介したい。

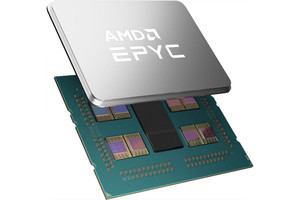

AMD Instinct MI250/250Xは2つのダイを1つのパッケージに収めたMCM構成である(Photo01)。

-

Photo01:Host I/FはPCIeとInfinityFabricのみで、CXLは未対応。まぁAMDのCPUとつなぐ限りにおいてはCXLをサポートする理由がないのだが。あと現状はPCIe Gen4対応なので、CXL 1.1/2.0の要求(PCIe Gen5対応)を満たさないという理由もある

Photo01ではShader Engineと書かれているものは、実際にはXCUという名称になっているが、ダイそのものはXCUが14×8で112XCU構成である。MI250Xはこのうち110XCUを有効にしたものを2ダイ、MI250は104XCUを有効にしたものを2ダイ、MI210は104XCUを有効にしたものを1ダイという構成になる。ダイサイズは公開されていなかったと思うが、TSMC N6で580億トランジスタだから相応の大きさになる。公開されたCG映像からの推定でも700平方mmを超えるサイズになっている。

ここで2つのダイはTSMCのCoWoSベースのInterposerで接続されるのだが、従来のCoWoSの場合、ダイ全体を載せる形になるので、2つのダイだと合計1400平方mmを超えてしまい、Reticle Limit(Stepperで露光できるサイズの限界)を超えてしまう。TSMCではCoWoSで2500平方mmに達するサイズまでを可能にする技法を昨年のECTCで発表しているが、これは要するに配線密度を犠牲にする方法であって、どんな場合でも使える訳ではない。そこでAMDはInstinct MI250/250Xでは2.5D EFBを採用してこれに対応している。

-

Photo02:2.5D EFBとは、要するにダイ間接続とかダイ/HBMの接続部分には普通にSilicon Interposerを置いてこれで接続。一方そうした接続を行わない部分(外部への信号とか電源/GND)に関しては、Silicon Interposerと同じ厚みの銅のVIAを置き、これで高さを揃えるという方法。要するにIntelのEMIBの逆パターンである

さて性能では、初代のInstinct MI100と比較して、おおよそ2倍の性能/消費電力比を誇っている(Photo03)。

動作周波数は大きくは違わず、違いは主に演算ユニットの数と、対応する演算の種類の増加である。

Photo04がXCUの構造であるが、元々MI100では

- Vector:FP32/FP64

- Matrix:FP16/BF16/FP32

の演算が可能だった。これに対しMI200では

- Vector:FP32/FP64

- Matrix:FP16/BF16/FP32/Packed FP32/FP64

とMatrix側で対応できるデータ型がかなり強化されているし、Vector Unitそのものの演算性能もMI100世代から倍増している。

動作周波数そのものはそう上がっていないが、プロセス微細化の効果もあって演算ユニット総数は倍増しながら消費電力はほとんど変わらず、その結果として2倍の性能/消費電力比を達成できたという訳だ。

ところで次のスライドが今回初公開である。これはL2とHBM2e、それと2つのダイをどうつなぐかという話だが、L2とHBMの間にInfinity Fabricが挟まり、このFabric同士が相互接続されている格好だ。流石に帯域はHBM2eには及ばないものの、同期をとったり結果を送りだしたりするには400GB/secは十分な性能であり、あとはアプリケーション側の最適化さえ行われればうまく使えそうだ。このあたりの最適化はROCm次第ということになりそうだ。

-

Photo05:Infinity Fabricを経由すると流石に結構性能のペナルティが大きいので、NUMA的に「可能な限りローカルのHBM2eを使う」といった配慮が必要だが、ROCm的には異なるダイに対してROCmRDMAを行う形になるのか、それとも同じノード内のデバイスという扱いになるのか、どちらなのだろう?

さて、MI250Xの性能を示したのがこちら(Photo06)であるが、実はFrontierではもう少し性能が下がる。

2022年6月のTOP500でランキング1位を取ったFrontierの構成はこちらであるが、細かい計算は後でご紹介するとして、このTOP500に登録された数字で言えばInstinct MI250Xのピーク性能は45TFlopsと計算される。

Photo06の数字はピークの1.7GHz駆動ではなく、1.6GHzに動作周波数を下げて運用されている模様だ。消費電力はMI250Xが1個あたり500Wを切る程度、と推定されるため、性能/消費電力比は90GFlops/Wほどになる計算だ。なぜ動作周波数を下げるか? といえば、性能/消費電力比向上のためである。実際、Frontierはピーク1685.65PFlops、実効1102PFlopsを、21MWで達成している。元々DoE(米エネルギー省)がExascale Computingを2013年に立ち上げた時の目標は

- システムのピーク性能:1000PFlops

- システムの総消費電力:20MW以下(のちにこれは30MW以下に修正された)

- システム全体のメモリ:64PB以上

- システムのストレージ:500~1000PB

- I/Oの実効帯域:60TB/sec

- MTTI(平均修復時間):1日以下

となっている。Frontierは最初の2つの項目を見事に実現した訳だ。

ちなみにFrontierの総ノード数は9248と推定され、それぞれのノードには64コアEPYC+Instinct MI250×4という構成になっている。第3世代EPYCの場合。8chのメモリに最大256GB(3DS DIMM)を合計16枚装着できるので、最大4TB(ただしDDR4-2933扱い:DDR4-3200動作の場合はchあたり1枚なので最大2TB)、Instinct MI250Xは1枚あたり128GBなので、4つで512GBとなる。つまりノードあたり4.5TBという計算になり、メモリ容量は40PB強にしかならないが、これは将来CXL Memoryで増設するという技もある訳で、あまり大きな問題にならないだろう。

Frontierのノード構成はこんな感じ(Photo07)。

-

Photo07:NICはHPEのSlingshot-11である。こちらはホストと2×PCIe Gen4 x16で接続される。ただPCIeはこのSlingshotの接続のみに使われ、CPU-GPU/GPU-GPUは全部InfinityFabricでの接続である

ちなみにこの図だと2つのダイの片方だけがNICにつながっている様に見えるが、実際には2つのダイがそれぞれSlingshot-11につながっている。Slingshot-11そのものが2つのNICを1つのダイに収めた構成になっているからだ。このSlingshot-11の詳細は今年のHotInterconnectsで公開されたので、機会があればこちらも紹介したいところだ。そのFrontierは完全に液冷の構成になっており、2つのノードが1つの1Uラックに収まる格好になっている。

ちなみにノード数や動作周波数の推定であるが、TOP500の結果では総コア数が8,730,112とされている。Frontierの場合1ノードがEPYC+Instinct MI250X×4でEPYCが64コア、Instinct MI250Xが220コアだから、ノードあたり944コア。総コア数を944で割ると9248ノードとなる。またRpeakが1,685.65PFlopsとなっているが、これを9248で割ると、ノードあたり182TFlopsと、これも綺麗に割り切れる。EPYCは性能が1TFlops/GHzなので、要するに2GHzのEPYCが2TFlopsに45TFlopsのInstinct MI250Xが4つと考えるのが一番妥当である。EPYCも64コアだとEPYC 7713かEPYC 7773Xのどちらかで、多分7773Xを2GHzにダウンクロックし、Boostを無効化(その分消費電力を下げる)という感じだろう。またMI250Xも45TFlopsということは、上で書いたように1.6GHzに動作周波数を落としての運用と考えられる。

このシャーシを利用したシステムは、今年のTOP500で4サイトが登録されている。実は一番効率が良いのはFrontierの導入に先行してインストールされたFrontier TDS(Test & Development System)である。こちらは128ノードからなる小規模なシステムで、TOP500では29位でしかない。

ただこのサイト、Rpeak(理論性能)が23.11PFlopsに対してRmax(実効性能)が19.20PFlopsで、効率は実に83%。Frontierは65.4%ほどでしかない。差は何かと言えばネットワークである。128ノードなら小規模というか、Dragonflyトポロジーを取るまでもなく相互接続が可能な小規模Interconnectが可能だが、Frontierでは9248ノードを74グループに分割し、相互をDragonflyで接続する複雑なバックボーンInterconnectが必要になる。これが性能というか効率の低下と性能/消費電力比の悪化を招いているのが明白である。バックボーンInterconnect用の機材が多い事が、性能/消費電力比を2割ほど下げている、というのはなかなか興味深い。

ちなみにAMDはもう少し汎用向けの構成も提案しており、2CPU/4GPU構成(Photo10)の汎用構成とか、2CPU/8GPUのAI/ML向け構成(Photo11)なども提案している。このPhoto10に関してはGIGABYTEおよびSuperMicroより、実際の製品も用意されるようだ(Photo12,13)。

-

Photo10:CPU同士やGPU同士はInfinityFabricで接続するが、CPU-GPUはPCIeを使う方式。ただこれ、次世代のGenoaベースEPYC+RADEON Instinct MI300でCXLを使う様にしないと効率が悪そうである

新情報は少ないが、すでにTOP500に登録した(ということはほぼフルシステムでの稼働実績がある)事を背景にした、現実的な結果が示された内容になった。

-

Photo13:SuperMicroは3U構成。こちらはMI250のままだろう。Memory Population GuideそれはともかくAMDのMemory Population Guide(https://www.amd.com/system/files/TechDocs/56873_0.80_PUB.pdf)を見る限り、RDIMMでもDDR4-3200でchあたり2枚のDIMMはサポートしていないはずだが、これはSuperMicroが自身でサポートするという意味だろうか?