京都大学(京大)は、SiC半導体の集積回路を用いてSi半導体の集積回路では動作不可能な350℃という高温環境における基本動作の実証に成功したことを発表した。

同成果は、京大大学院 工学研究科の金子光顕助教、同・木本恒暢教授らの研究チームによるもの。詳細は、3月22日~26日に青山学院大学 相模原キャンパスとオンラインでハイブリッド開催されている「応用物理学会第69回春季学術講演会」において、3月25日に発表された。

Si半導体は約250℃で誤作動を起こすとされており、それ以上の高温環境での動作はできないとされている。そのため、より熱耐性に優れ、約800℃でも動作可能なSiCの集積回路の活用が期待されているが、Si集積回路のトランジスタと同様の構造をSiCで作製すると、SiC特有の欠陥により特性制御が困難となってしまい、高温環境における信頼性が確保できなくなるほか、消費電力も高くなることが課題とされていた。

こうした課題の解決に向け、Si集積回路のMOSFETとは異なる構造のSiC集積回路用トランジスタの開発が進められており、中でもJFETは電流が流れる領域にMOSFETのような界面欠陥が物理的に存在しないため、高温動作SiC集積回路を構成するトランジスタとして有望視されている。

しかし一般的な方法で作製したJFETは、MOSFETのように同一基板上でn型とp型を組み合わせた相補型回路の構成が不可能であることから、大きな待機電力が必要となり、低消費電力化が求められていた。

こうした背景の中、研究チームは今回、独自のトランジスタ構造および回路構成を提案。室温から350℃までのSiC論理ゲート動作実証、ならびに低消費電力での動作に成功したという。

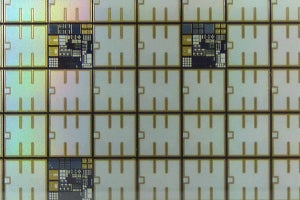

実現のポイントは2つ。1つ目は、これまでの一般的なJFETの作製方法では不可能だった、n型とp型の両方を同一基板上に作製する技術を実現したこと。デバイス構造すべてをイオン注入による局所的伝導型制御を行うことで、同一基板上へのn型とp型のJFETの作製に成功したという。

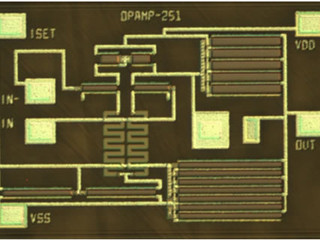

2つ目は、トランジスタの特性として、ゲート端子に電圧を加えていないときは電流を流さないノーマリーオフ型の特性をJFETで実現した点だという。この特性も一般的なJFETの作製方法では実現が難しいとされるが、チャネル領域を両側から挟み込む形でゲート領域を構成するダブルゲート構造とすることで、ノーマリーオフ型のJFETの作製が実現されたという。

作製された相補型JFETは室温から350℃の温度範囲で正常に動作し、待機状態の消費電力は最大でも数十nW以下に抑えられることが確認されたとする。

なお、今回の研究成果は、パワー半導体として用いられているSiC半導体の標準的なプロセスを用いることで、今回提案の回路を作製できることがメリットだと研究チームでは説明しているが、MOSFETで進められてきた微細化による小型化、高速化、高機能化がJFETでも可能かどうか、さらなる基礎研究が必要であり、引き続き検討を進めていく必要があるともしている。