Opteron以来、長い間、AMDはサーバ市場でIntelのXeonに対抗できる製品を持っていなかったが、ZenアーキテクチャのEPYCプロセサでサーバ市場に戻ってきた。EPYCはサーバ向けに最適化されたプロセサであり、巨大データセンタでの採用が始まっている。

このEPYCプロセサについて、COOL Chips 21にて、AMDのシニアフェローのJay Fleischman氏が基調講演を行った。

Zenアーキテクチャを採用したEPYC

EPYCは、AMDがゼロから新設計したZenマイクロアーキテクチャのサーバ用プロセサである。ZenマイクロアーキテクチャのプロセサはAMDの前世代のExcavatorプロセサに比べて52%ほどIPC(Instruction per Cycle)が高いという。

Bulldozerに始まる建設機械シリーズのプロセサは1コア、1スレッドであったが、Zenでは、IntelのXeonと同様に、1コア、2スレッドのSMT(Simultaneous Multi-Thread)実行になった。IPCの向上は、このSMT化が大きく貢献しているのではないかと思われるが、データセンタとしては処理あたりのコストが重要であり、なにによってプロセサ性能が上がっても構わない。

-

Zenは、データセンタ向けにゼロから作り直した新マイクロアーキテクチャで、前世代のAMDのプロセサと比べてIPCが52%高い (このレポートのすべての図は、COOL Chips 21におけるAMDのJay Fleischman氏の講演スライドのコピーである)

Zenは、4つの整数演算ユニット、2つのロードストアユニット、2つの浮動小数点演算ユニットを持ち、命令キャッシュは64KB 4way、D1キャッシュは32KB 8way、L2キャッシュは512KB 8wayである。そして、4つのコアで共用される8MBのL3キャッシュがある(どのコアからもシステム内のどのL3キャッシュスライスにもアクセスできるので、この記述は正確ではないが、後述のように4コアと8MBのL2スライスが一体に作られているので、このように表現している)。さらに、展開されたマイクロ命令を格納するOPキャッシュを備えている。OPキャッシュの容量は2Kマイクロ命令である。

-

Zenコアは、従来のAMDのプロセサと異なり、2スレッドを並列に実行するSMTになった。Zenコアは、4つの整数演算ユニット、2つのロードストアユニット、2つの浮動小数点演算ユニットを持ち、64KBの一次命令キャッシュ、32KBの1次データキャッシュ、512KBの2次データキャッシュを持つ。そして、4コアグループごとに共通の3次キャッシュを持つ

前述のように、Zenは2スレッドを並行して実行するSMTプロセサである。次の図は、ブロックダイアグラムに書かれた各ユニットが、どのように2つのスレッドで使われるのかを示すもので、白色に塗られた3つのキューだけはエントリをスレッドに割り当て排他的に使用する方式となっている。それ以外のユニットは2つのスレッドで使用権を取った方のスレッドが使用するという競合的共有となっている。

なお、1スレッドしか実行していない状態では、そのスレッドが全資源を使うことができ、使えない資源が残ることはない。

Zenのレイアウト

Zenのキャッシュ階層は次の図のようになっている。L2キャッシュはコアごとに設けられており、アクセス時間は12サイクルである。4コア共通のL3キャッシュのアクセス時間は35サイクルである。キャッシュミスが発生しても、下位のキャッシュ、あるいはメモリアクセスと並行して後続のメモリアクセス命令の実行を続行するノンブロッキングキャッシュは多くのプロセサで使われているが、Zenはサーバ用プロセサであるので、多くのミスを記憶するバッファを持っている。L2キャッシュのキャッシュミスについては50回、L3キャッシュのミスは96回分のバッファがあり、この範囲内であれば、後続のメモリアクセス命令を処理し続けることができる。

-

1次キャッシュは、命令キャッシュとデータキャッシュがあり、2次キャッシュは命令、データ共通のキャッシュである。3次キャッシュは4コアで共有の命令、データ共通のキャッシュである。L3キャッシュは8MBで、2次キャッシュを追い出されたデータを格納するビクティムキャッシュである。サーバ向けであるので、2次キャッシュミスのバッファは50エントリ、3次キャッシュミスのバッファは96エントリあり、ミスの処理中も後続のメモリアクセス命令の処理を続ける

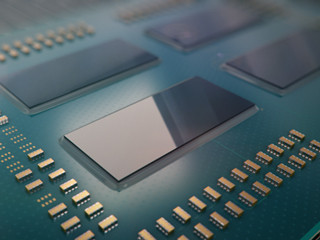

Zenは、物理的には4コア単位でレイアウトされており、8MB 16wayのL3キャッシュが付いている。AMDは、これをCCX(CPU CompleX)と呼んでいる。

L3キャッシュは4つの2MBのスライスで構成されており、下位のアドレスビットでインタリーブされている。そのため、どのコアがどのスライスをアクセスする場合も、平均アクセス時間は同じである。

なお、L3キャッシュはビクティムキャッシュであり、L2キャッシュを追い出されたデータを格納する。

-

4コアと8MBの3次キャッシュのまとまりが物理的なレイアウトの単位であり、AMDはCCXと呼んでいる。4つの3次キャッシュスライスはインタリーブされており、どこをアクセスしても平均アクセス時間は同じである

次の図はIntelのSkylake-SPとAMDの前世代のBulldozerファミリとZenの諸元を比較したものである。左がキャッシュ系の表で、容量やアクセスレイテンシを比較している。右はプロセサコアの表で、レジスタ、リオーダバッファ、演算器を比較している。

この表を見ると、ZenはSkylake-SPと比較してL2、L3キャッシュのアクセスが速い点とFP演算の幅が128bitでAVX-512を1サイクルでは実行できない点が目を惹く。

Zenは、ECCで訂正できないメモリエラーが見つかっても、CPU全体を止めるのではなく、そのデータを使うプロセスだけをKillするData Poisoningをサポートしている。また、ハイパーバイザを効率的に動かすためのNested Virtualization、SpectreやMeltdown攻撃でメモリ上のデータが盗まれても、内容が分からないようにする自動暗号化などのサーバ向けの機構を強化している。これらはBulldozerには無かった機能である。

エラー訂正の観点では、ZenのL1DキャッシュにはSEC-DED ECC(シングルエラー訂正、ダブルエラー検出)が付けられており、L2、L3キャッシュにはDEC-TED ECC(ダブルエラー訂正、トリプルエラー検出)が付けられている。 DRAMはx4のDRAMチップが全ビットエラーしても訂正できる機能を持ち、コマンドやアドレスもパリティチェックで保護されている。