U.C.DavisのKiloCoreプロセサ

一方のU.C. DavisのBaas教授のグループが発表した1000コアを集積するKiloCoreチップは、その名の通り1000コアを集積している。

|

|

KiloCoreを発表するU.C.DavisのBrent Bohnenstiehl氏 |

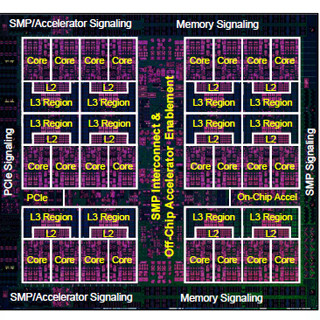

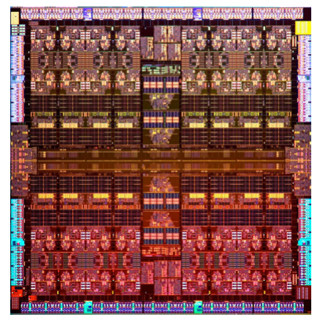

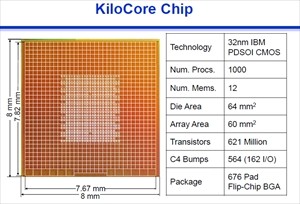

IBMの32nm FD-SOIプロセスを使用し、8mm×8mmのチップに621Mトランジスタを集積している。チップ写真の上側に31列32行のコアがあるが、これでは992コアにしかならないので、下辺の6+6のメモリタイル(大きめの箱)の間に8コアを追加して1000コアとしている。

|

|

KiloCoreチップのダイ写真と諸元。IBMの32nm FDSOIプロセスを使い1000コアを集積している (このレポートのすべての図は、Hot Chips 28でのBohnenstiehl氏の発表スライドのコピーである) |

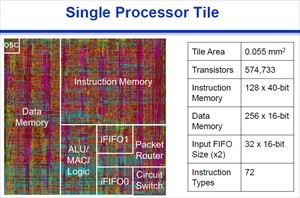

個々のプロセサタイルは0.055mm2で128ワード×40bitの命令メモリと256ワード16bitのデータメモリがタイルの大部分の面積を占めている。

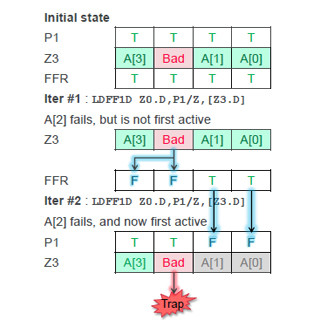

また、後述のように、タイル間の通信は非同期になっているので、FIFOを使ってメッセージの到着タイミングの違いを吸収していると思われる。

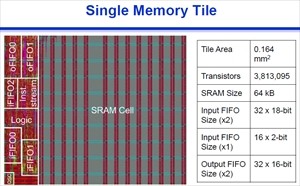

次の図は、チップの下辺に置かれているメモリタイルの拡大写真である。タイルの面積は0.164mm2で64KBのSRAMを持つ。KiloCoreチップは、このメモリタイルを12個持っている。

KiloCoreはコアごとに独立の命令を実行できるMIMD方式のプロセサである。しかし、その設計思想は、いわゆる汎用プロセサとはかなり異なっている。各プロセサの命令メモリは128ワード×40bitで、基本的には128命令しか格納できない。データメモリは256ワード×16bitである。そして、プロセサ間のデータの受け渡しはパケット化されたメッセージとして受け渡される。

ただし、メモリタイルに隣接したプロセサ間ではメモリタイルをシェアードメモリとして使い、データの受け渡しができるようになっている。

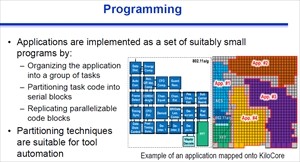

このように少ない命令メモリとデータメモリでどのようにデータを処理するのかというと、各コアが1つの仕事を丸ごと実行するのではなく、多数のコアを使い、各コアはストリーム的な処理の1ステップだけを担当するという処理モデルになっている。

次の図の中央付近に書かれているのは802.11a/gのWi-Fiの処理であるが、22コアとそれ以外にViterbiデコードとFFTの処理が必要になっている。これらすべてを含むと右端の図のようにチップの左下の60個余りのプロセサタイルと2個のメモリタイルを必要とする。

このように処理を細かく分割しているので、1つのプロセサタイルでは最大128命令、256ワードのデータメモリで処理ができる。

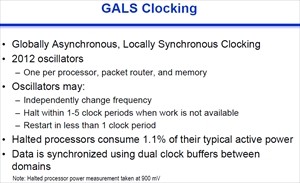

タイルの内部は同期であるが、タイル間は非同期で動作するGALS(Globally Asynchronous Locally Synchronous)という方式を使っている。このため、プロセサやパケットルータ、メモリのそれぞれがクロックの発振器を持っており、チップ全体で2012個の発振器を使っている。

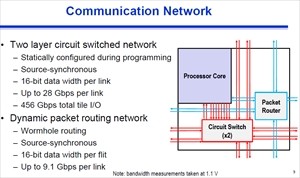

プロセサタイルは、2層の回路スイッチネットワークと1つのパケットルータを持っている。回路スイッチのバンド幅はリンクあたり28Gbps、パケットルータはリンクあたり9.1Gbpsのバンド幅を持っている。

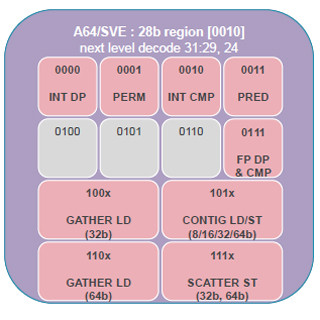

プロセサは7段のパイプラインで、命令長は40bitで、シングルイシューのインオーダ実行である。データパスは16ビット幅である。