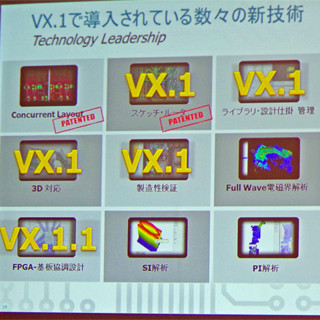

ケイデンス・デザイン・システムズ(ケイデンス)は1月20日、Sigrity 2016テクノロジー・ポートフォリオの提供を開始すると発表した。

Sigrity テクノロジー・ポートフォリオは、バーチャルUSB3.1チャンネルのバリデーションを行うIBIS-AMI モデル自動生成のサポート、複数のフィールド・ソルバーを使用した高速かつ高精度なチャネルモデル抽出、電源を考慮したシグナル・インテグリティー解析レポートを含むため、フィジカル設計のUSB-IF (USB Implementers Forum) コンプライアンステスト向けの認定を迅速に取得することができ、各種技術と併用することで、設計プロセスの数週間単位での短縮できるとしている。

今回発表されたSigrity 2016テクノロジー・ポートフォリオでは、ケイデンスの設計IP SerDes PHY チームが使用している確認済みの各種イコライゼーションアルゴリズムを積極的に活用、アルゴリズムを実行可能モデルに統合し、パラメタライズやコンパイルを自動化するためのメソドロジーを提供。これにより、SerDes I/O モデルの開発を効率よく行うことが可能となった。

また、ハイブリッド・ソルバーと3D フルウェーブフィールド・ソルバーの併用によって、高精度チャネルモデルを10倍高速に生成する機能を有しているほか、手作業の介入が最小限となったことにより、シリアルリンクチャンネルをセクションに分割し、各セクションを解析してから自動的に1つのインターコネクトモデルにまとめることができるようになった。さらに、高速なモデル抽出手法により、さまざまな信号配線と層変更のトレードオフ解析を実現し、同時に厳しいTAT要件を満たすことも可能となっている。

同テクノロジー・ポートフォリオについてケイデンスは「マルチギガビット・インターフェースに理想的な、強化されたPCB設計手法および解析手法を使用して製品の製作期間を短縮できます。」とコメントしている。