今年のHot Chips 27でもっとも意外感のあった発表は、中国のPhytium Technologyという会社の「Mars」と呼ぶ64コアのARMv8プロセサの発表であった。発表を行ったのは同社の研究部長のCharles Zhang氏であるが、米国のビザが得られなかったため会場には来られず、スライドと電話での発表となった。

Phytiumは2012年に創立された会社で、広州と天津にオフィスを持つ。同社のWebサイトでは高性能サーバ向けのマイクロプロセサやアクセラレータ、リファレンスボードなどのテクノロジを供給すると書かれている。しかし、具体的にどのような開発をやっているのかはまったく情報が無く、今回のHot Chipsが初めての発表である。

同社はハイエンドのMarsと呼ぶプロセサとクラスタ型サーバ用の「Earth」というプロセサの開発を行っているが、今回の発表はMarsに関するものである。

ARMv8準拠の64コアプロセサ

MarsのコアはARMからARMv8のアーキテクチャライセンスを受けて開発しており、命令レベルではARMv8準拠である。Marsチップは、8コアをまとめたパネルという単位を8個使って、全体で64コアになっている。そして、各パネルにはCMCと呼ぶ16MBのL3キャッシュとDDR3-1600のDRAMチャネルを2チャネル集積するチップが接続される。つまりフル構成では、CPUを含めて、17チップと最低16枚のDIMMを必要とするという大きなシステムとなる。

Marsチップは28nmプロセスで作られ、2.0GHzクロックで動作し、消費電力は120Wである。集積度は約180Mインスタンスと書かれているが、各インスタンスがどの程度のトランジスタ数であるのかは不明で、SRAMマクロも2入力NANDも1インスタンスとするとあまり意味のない数字である。

浮動小数点演算性能はピークで512GFlops、メモリバンド幅は204GB/s、I/Oバンド幅は32GB/sとなっている。

|

|

Marsシステムの構成。8コアを含むパネルを8枚持ち、各パネルにCache and Memoryチップが接続されている。2GHzクロックで動作し、消費電力は120W (以下の図はすべてHot Chips 27でのPhytiumの発表スライドのコピーである) |

DDR3を16チャネル持っているのでメモリバンド幅は大きく、メモリバンド幅と演算性能の比であるB/F比は約0.4Byte/Flopであり、最近のプロセサとしては比較的高い値になっている。

なお、現在は設計が終わった状態で、まだ、テープアウトされていないとのことで、クロック周波数や消費電力は、同社の見積もりである。

Xiaomiコアは独自設計

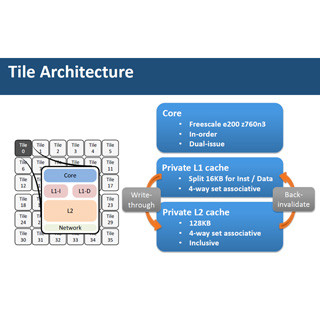

次の図はパネルの内部構成を示すもので、8個の「Xiaomi」と呼ぶコアを集積している。ARMv8のアーキテクチャライセンスを受けており、Xiaomiコアは64bit ARMアーキテクチャのコアとなっている。

アーキテクチャライセンスの場合は、ARMの論理設計には縛られず、独自に論理設計を行うことが認められており、高性能コアを作ることができる。Xiaomiコアは、4命令フェッチ、デコード、ディスパッチのOut-of-Orderと書かれており、本家のARM Cortex-A72が3命令デコードであるのに比べて、より並列度の高い設計になっていることが注目される。

パネルは4個のXiaomiコアが2MBのL2キャッシュを共用し、キャッシュのコヒーレンスを維持するDirectory Control Unit(DCU)に接続されている。これが2組あり、パネル全体では8コア、4MB L2キャッシュという構成になっている。そして、ルーティングセルを経由して他のパネルやメモリと繋がっている。

パネルの大きさは6mm×10.6mmとなっており、1個のコアあたり約8mm2の面積を占めている。これは、TSMCの16FF+プロセスで作ったCortex-A72が1.15mm2と言われるのと比べると、微細化の程度の違いを補正しても3倍程度の面積と思われる。

Xiaomiコアは、32KBのL1命令キャッシュと32KBのL1データキャッシュを持ち、整数/分岐、整数×3、浮動小数点×2、ロード/ストアの計7本の実行パイプラインを備えている。そして、4つの命令デコーダを持ち、最大4命令を並列に処理できる構成になっている。