東芝は2月22日、スマートフォンなどの携帯機器向けシステムLSIに混載されるSRAMの消費電力を大幅に削減する回路技術を開発したと発表した。

詳細は米国サンフランシスコで開催された「ISSCC 2013(International Solid-State Circuits Conference:国際固体素子回路会議)」にて発表された。

一般にLSIの論理回路は、電圧を下げると動作電力を低減できる傾向にあるが、SRAMは電圧を下げると逆に動作電力が増加する場合があり、最小となる電圧が動作条件によって異なるため、動作電圧を最適化することが困難だった。また、SRAMはシステムLSIの待機電力の大半を占めており、待機電力を低減するためには常時SRAMに電力を供給しているアナログ式電圧制御回路の電圧制御アンプの消費電力を削減することが課題だった。今回、そうした課題の克服に向けて、ビット線電力計算器および、デジタル制御リテンション回路を適用した混載SRAMを開発したと同社では説明する。

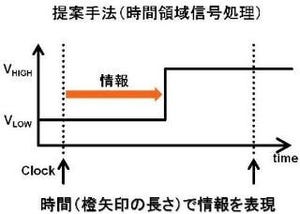

SRAMにはビット線と呼ばれる読み出しデータ転送用の配線があるが、今回は、このビット線を利用したクロック生成回路と、このクロック周波数をモニタする回路で構成されるビット線電力計算器を搭載することで、従来では困難だったビット線の動作電力予測を可能にしたとのことで、これによりビット線の動作電力とそれ以外の回路で消費される動作電力の合計が最小となるように電圧を選択することが可能となり、動作条件に応じた最小電力でSRAMを動作させることができるようになるとする。

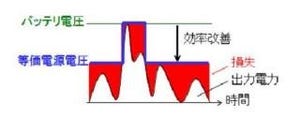

また、待機電力対策として、SRAMの電圧制御回路にデジタル方式を採用したデジタル制御リテンション回路を開発。これにより、SRAMに電圧を供給する電圧制御バッファのサイズ情報をデジタルで保持できるようになるため、周期的に電圧制御アンプを起動しバッファサイズを更新することで、電力の削減が可能になったとするほか、複数のSRAM間で同一の電圧制御アンプを共有し、順次バッファサイズ情報を更新することで従来のアナログ方式に比べて電源制御回路の面積増大を最小限にとどめることが可能になったという。

なお試作チップを用いた試験では、25℃環境下での動作時に、従来技術比で動作電力を27%、待機電力を85%削減できることが確認されたとのことで、同社では今後、より低消費電力なLSIの実現に向け、今回開発したSRAM技術のデジタル機器への適用に向けた技術開発を進めていく方針としている。