産業技術総合研究所(産総研)は12月12日、特性バラつきが世界最小クラスの14nm世代立体型トランジスタ(FinFET)を試作したと発表した。

成果は、同所 ナノエレクトロニクス研究部門 シリコンナノデバイスグループ 松川貴主任研究員、昌原明植研究グループ長らによるもの。詳細は、2012年12月10日~12日に米国サンフランシスコで開催された国際会議「2012 International Electron Devices Meeting(IEDM 2012)」にて発表された。

2017年以降に市場投入が想定されている14nmプロセス世代のトランジスタでは、その寸法の小ささからトランジスタ素子間の特性バラつきの問題が大きく顕在化してくると考えられており、製品の性能向上の阻害と歩留りの低下が懸念されている。とりわけ、システムLSIやマイクロプロセッサの50%以上の面積を占めるSRAMでは、最小寸法のトランジスタを多用するため、特性バラつきの影響を受けやすいため、特性バラつきの少ない微細トランジスタの開発が強く求められている。

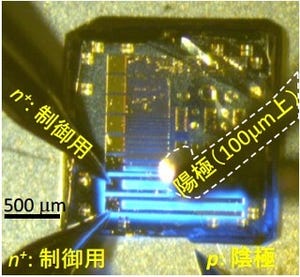

産総研では、3次元立体構造にしたFinFETの研究を推進してきており、これまでの研究にて、素子特性を電気的に制御するための端子が付加された4端子型FinFETを提案し、2003年に動作検証に成功し、2008年にFinFETにおける新たな特性バラつき要因として、金属ゲート電極材料の物性のバラつきを提唱したほか、物性バラつきを低減できるトランジスタ作製技術を提唱していた。また、14nm世代FinFETのオン電流バラつきの主な要因を解明し、その後もFinFETの特性バラつきを抑えるための研究開発などを進めてきていた。

トランジスタの微細化によって顕在化する特性バラつきは、大きく分けてオフ電流バラつき、オン電流バラつきとなって現れ、集積回路の性能に悪影響を与える。オフ電流バラつきにより、集積回路チップ中の一部のトランジスタのオフ電流が設計値に比べ指数関数的に増加し、このためにチップ全体の待機時消費電力が増加してしまう。集積回路の動作速度は、回路を構成する最もオン電流の低いトランジスタにより制限されてしまうため、オン電流バラつきにより、設計値よりも回路の動作速度が低下する。つまり、トランジスタの微細化を進めたにもかかわらず、動作速度が向上せず、しかも消費電力が増加するという深刻な問題が発生してしまう。

22nm世代以降に導入が始まったFinFETでは、特性バラつきの主な要因はゲート電極の仕事関数という物性のバラつきである。トランジスタの重要な電気的特性であるしきい値電圧は、金属ゲート電極材料の仕事関数によって決まる。一般に用いられる金属ゲート電極材料は多結晶構造で、個々の結晶粒の界面(結晶粒界)ごとに仕事関数がばらついているため、しきい値電圧にバラつきが発生する。

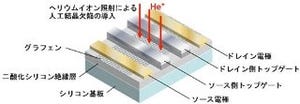

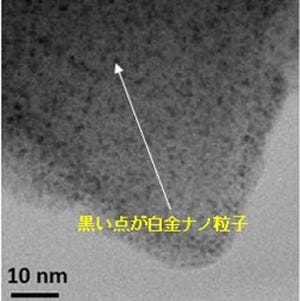

そこで、通常の多結晶金属(TiNなど)の代わりに、結晶粒界を持たない非晶質金属材料(TaSiN)をゲート電極材料として用いて、電気的特性バラつきの比較を行った。図3は、今回開発された非晶質TaSiN金属ゲート電極を持つフィン断面の電子顕微鏡像と、従来型多結晶TiN金属ゲート電極との比較。非晶質TaSiN金属ゲート電極はフィンチャネルの側壁に均質に成膜されており、TiN電極のようなバラつきの原因となる結晶粒界は見られない。また、TiN電極では結晶構造を反映して周期的で離散的なスポットパターンの電子線回折が観測されるが、TaSiN電極では周期性がないことを示すぼやけたリング状の電子線回折パターンが観測され、非晶質TaSiN金属ゲート電極がフィンチャネル上に適切に形成されていることがわかる。

作製されたFinFETについて、さまざまな設計寸法の素子の電気的特性バラつきのうち、しきい値電圧バラつきと相互コンダクタンスバラつきの2つのバラつきの解析を行ったところ、図4のようなしきい値電圧バラつきに関するPelgromプロットが得られた。プロットの傾きが小さいほど特性バラつきが小さいことを示しており、非晶質TaSiN金属ゲートを用いることで、多結晶金属ゲートに比べて、しきい値バラつきを大きく低減でき、これまで報告されているFinFETの値の中で最小値となる1.34mVμmを示したという。この値は、図1右で確認できる通り、15nm世代のSRAMの正常動作に必要とされる値を満たしており、これによりトランジスタ微細化に伴う、しきい値バラつきの顕在化を抑制する技術にブレークスルーをもたらすことが可能になったと言える。

図5は、ゲート長100nmと50nmの場合の、相互コンダクタンスバラつきの比較。しきい値電圧バラつきと同様に、ゲート長縮小により相互コンダクタンスバラつきが増加するが、非晶質金属ゲート電極の導入により、バラつき増加を抑制できる。相互コンダクタンスバラつきは、14nm世代以降のトランジスタのオン電流のバラつきの主な要因として顕在化するため、非晶質金属ゲート電極を用いたFinFETは14nm世代以降のオン電流バラつき問題の解決に有効と考えられる。さらには、SRAMをはじめとする集積回路の歩留りが低下する問題や、集積回路の性能向上と低消費電力化の限界の解決につながると考えられる。

なお、同技術はデバイスメーカーのみならず、半導体製造装置メーカー、材料メーカー、計測評価機器メーカーなどでも活用することができることから産総研では、企業への技術移転や協働も念頭に研究を推進中としている。また今後は、FinFETを用いた集積回路を作製し、回路レベルでの低消費電力化と歩留まり向上の実証を目指すと研究グループではコメントしている。