Intelの日本法人であるインテルは8月31日、新成長分野に対する戦略を立案する100%子会社「Intel Federal」を設立したことを発表し、同日、都内で同社のデータセンターおよびHPC分野に対する取り組みの説明会を開催した。

新会社は、米国エネルギー省やその他の団体と共同で推進するエクサスケールコンピューティングを含む、HPCセグメントに関連した活動に注力する予定で、米国政府のすべての省庁との協力案件の検討なども行っていく予定。

Intelの副社長兼データセンター・コネクテッド・システム事業部長のKirk Skaugen氏は、「Intelは、(2010年に)"クラウド2015ビジョン"を掲げ、インターネットのトラフィック増加などの課題に対し、企業のIT部門が解決する支援に向けた取り組みを進めている」と説明。

また、同時期に設立され、同社がテクニカルアドバイザとして参加している「Open Data Centor Alliance(ODCA)」は、このほぼ1年の間に参加企業が当初の70から280以上に拡大し、オープンなデータセンター構築に向けた8つの利用モデルの定義や、クラウドに対するユーザーニーズの文書化、クラウド普及の妨げになっている緊急性の高い課題に対する解決策の検討などが進められており、「より多くの日本企業がODCAに参加してもらって、ニーズなどを日本から発信してもらいたい」と積極的な日本企業の参加を促す。

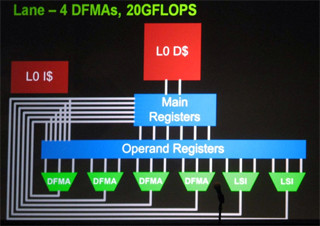

一方のHPC分野では、「Intel Many Integrated Core(MIC) Architecture」ベースの製品とXeonプロセッサを組み合わせることで、2018年までにExaスケールのスーパーコンピュータを実現するとする。

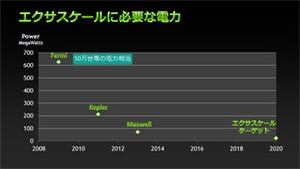

Exaスケール実現の最大の障壁となるのは電力消費量だが、2018年における同社の見立ては30~40MW(DARPAのUHPCプロジェクトでは当初2018年で20MWを目標としていたが、最近は2018-20で20MWとしている)だが、現状のアーキテクチャを考えるとそれでもかなり挑戦的な値といえる。このコアとなるのはMICアーキテクチャであり、それを支えるのがIntel Federalであるという。

「Intel Federalは世界最高のスパコンを作り上げることを目的として米国政府と協力して立ち上げた」と米国政府との緊密性をアピールするが、その一方で、「もちろん、米国だけでなく、他国の政府とも協業していくつもりもある」と、それだけではないことも説明することを忘れなかった。

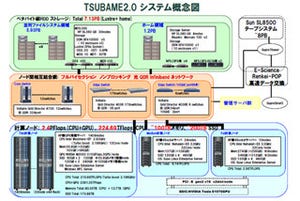

MICアーキテクチャを実装したKnights Ferryはすでに各国の研究機関などに提供されている。日本でも東京大学に提供され、ソフトウェアの開発などが進められている。

実際にKnights Ferryを用いている同大大学院情報理工学系研究科コンピュータ科学専攻の石川裕教授は、「メニーコア搭載クラスタによる高性能計算環境の開発を進めており、MICアーキテクチャによる浮動小数点演算処理のやり方も考える必要があるということで研究している」と説明する。

その背景には、アクセラレータ的に活用できるPCI Express対応カードとして現状入手可能なのはNVIDIAのGPUを搭載したものがKnights Ferryのみであり、GPUはそれ単体で動くアプリを作るのが難しく、「我々の目標にマッチしたのがMICである。また、x86アーキテクチャで各コアが構築されているので、Knights Ferryと各PCをシームレスにつなげ処理を行うこともできる。さらに、オープン性の観点を考えると、我々はOSを独自に開発しているが、その際にシステムアーキテクチャが開示される必要があり、Intelからはそれらの情報を開示してもらっており、それを元に開発を進めている」という研究の目的によりマッチしたものを選択した結果であることを強調する。

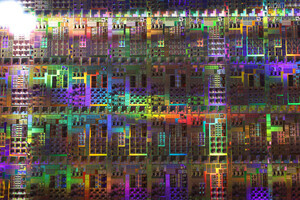

なお、同会見では最後にXeon-EP(Sandy Bridge-EP)とItaniumに関するアナウンスも行われた。Xeon-EPはSandy Bridge同様、最大1ソケット8コアに対応し、AVXを活用することで、浮動小数点演算性能を従来比で2倍に向上させることが可能。また、PCI Expressの統合によるレイテンシと消費電力の削減が図られているほか、6Gbps SASをプラットフォームに統合し、ローカルメモリのパフォーマンス向上も図られている。

一方のItaniumは、32nmプロセスを採用したPoulsonを2012年に投入する計画。8コアで、54MBのオンダイ・キャッシュ(50MB SRAM)、31億トランジスタとなる予定とするほか、その後継となるKITTSON(開発コード名)についても、「Itaniumについては2年サイクルで製品投入を図る計画」としており、今後も継続してサポートしていくとした。