2011年の1月31日から2月3日に掛けて、Santa Clara Convention Centerで開催されたDesignCon 2011において、Rambusは"Advanced differential signaling for SoC-to-memory interfaces"と呼ばれる新しいメモリ用のデータ転送技術(というか、あたらしいメモリインタフェース)を発表したが、2月9日、同社東京オフィスにおいて、その発表内容を改めて説明した。説明を行ったのはお馴染みRAMBUS本社のSteven Woo博士である(Photo01)。

|

|

Photo01:Technical Director, RambusのSteeven Woo博士。直前に居たベイエリアは摂氏23℃とかだったのが、東京に着いてみると雪模様。おまけに次は気温が-3℃とかいう韓国に行くことになっているそうで、「どうなってるんだ」とぼやくことしきり |

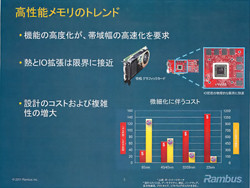

さて、今回の同社の発表は、先にもちょっと触れたマルチモードメモリコントローラである。まず最初に現在の、特にGPUとかGame Consoleといった場面での問題に触れ、特にGDDR5を使うアプリケーションではいずれも帯域が頭打ちになりかかっていること、それと今後の設計ではデザインコストが大きなボトルネックになりつつあることを示した(Photo02)。

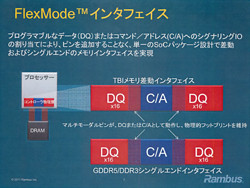

最初の問題は良いとして2つ目の話は、設計コストの増大によりASICを気軽に作れなくなってくる(というか、今でも130nm世代に比べるとかなり敷居が高いのだが)ために、なるべく1つのデザインで複数の用途に使いまわせるような配慮が求められてくる、という意味だ。この結果、特にGPUにおいては1つのGPUコアに複数種類のメモリを使うことが求められるようになる、とする(Photo03)。

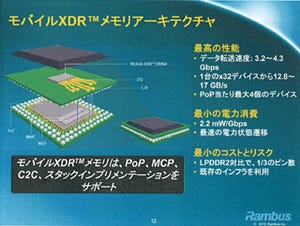

こうした機器の要求に対応できるようにするのが、今回発表された新インタフェースである(Photo04)。まず互換性という観点では、新インタフェースはXDR/XDR2で使われるDifferentialと、DDR3やGDDR5で使われるSingle Endedの両方の伝送方式に対応した点が新しい。また性能の観点でも、XDRやXDR2(というかTBI:Terabyte Bandwidth Initiative)で使われるDifferentialで20Gbps(従来はXDR2で16Gbps)、Single Endedでは最高12.8Gbps(従来はGDDR5で概ね6Gbps)までと、大幅に従来の転送速度の限界を引き上げたのが特徴である。またこれが極めて省電力なのも特徴で、Differentialでは20Gbpsで6mW/Gbps、Single Endedでも12.8Gbpsの場合にほぼ同等の消費電力だとか。ただSingle Endedに関しては12.8Gbpsまではこれで行けても、これを超えると急に消費電力があがるという話であった。

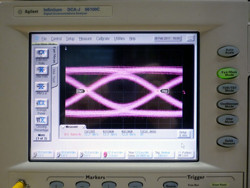

DesignCon 2011には、実際にこのコントローラを搭載した同一の試作シリコンを3つ搭載し、3種類のメモリをそれぞれ接続して転送デモを行っており(Photo05)、今回は会場にこれが持ち込まれて実機デモも行われた(Photo06~Photo10)。

|

|

|

Photo07:これはDDR3チップを接続しているもの。等長配線の様が良くわかる |

Photo08:こちらはGDDR5チップを接続したもの。こちらも等長配線が結構うねっているのがわかる。チップに隣接して接続していても、等長配線を実現するためには結構な配線面積が必要、というのがここからもわかる |

|

|

|

Photo09:こちらはTBI接続のケース。左のチップはXDR2(というか、TBI)メモリチップをエミュレートする回路 |

Photo10:これはSingle Endedで最大12.8Gbpsの転送を行っているデモ。振幅は300mV弱といったところである |

ところで単に二個イチではない、という話はこちらのFlexModeと関係する。例えば16bit幅を実現しようとした場合、Single Endedならば16本、Differentialでは32本の信号線がそれぞれ必要なわけであるが、実はこれ以外にもStrobeだのClockだのCommandだのとさまざまな信号線が別途必要である。DDR系の場合、16bit幅であれば44本の信号線が必要になるが、XDR系のDifferentialの場合はこうした制御信号が高度に多重化されていることもあり、必要な信号線の総数は殆ど変わらない。そこで一部のピンをMulti-Modalとすることで、ピンの本数を抑えることができるという仕組みだ(Photo11)。これにより、同一パッケージでSingle Ended/Differentialで別々のピンを用意せずに済む、というのがRambusの主張である。