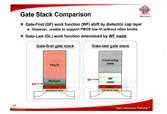

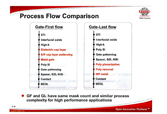

また、28nmプロセス以降についてはというと、「HKMGにはゲートファーストとゲートラストの2つの形成手法が考えられているが、我々も当初はゲートファーストを検討していた。しかし、NチャネルとPチャネルの性能を維持するためには別々の材料が必要となる。ゲートファーストは2つのチャネルは同じ材料を使うため、その制御が難しい。キャップレイヤを調整して対応しようという動きもあるが、必ずしも上手くいくとは限らない。また、高温アニールを行う際、ゲートファーストではゲートがすでに形成されており、そこでアニーリングの影響が出る危険性もあったことから、最終的にはゲートラストを採用した」(同)と解説、現状、28LPプロセスで64MビットのSRAMを形成した場合の歩留まりで65%を達成して、すぐにでも使える状態になってきていることを強調したほか、28HPでも同SRAM形成の歩留まりが26.8%、28HPLで同15%という状況になっており、「提供開始の時期までにはある程度まで歩留まり率を向上させる道筋はすでについている」(同)と、順調な仕上がり具合をアピールした。

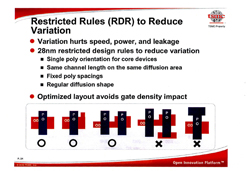

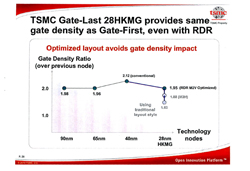

この28nmプロセスには、レイアウト手法として新たに「Restricted Rules(RDR)」を採用した。これについて同氏は、「我々がゲートラストの構造を採用したため、レイアウト手法を変えたように言われることがあるが、それは間違い。パフォーマンスの向上とプロセス管理を向上させて、歩留まりを高めようとした結果、RDRを導入するに至った。28nmプロセスにおけるゲート密度のレシオは、90nmで1.98、65nmで1.96、40nmで2.12と高めてきたが、そのまま既存のレイアウト手法を用いた場合、1.60に低下し、既存プロセス比で40%程度のペナルティを受けることとなる。RDRを導入することで、これを1.95まで引き上げることができ、そうしたペナルティをほぼなくすことができる」とし、レイアウト手法の改変に対応できるよう、ツールベンダと一緒に検証作業を進めているとするほか、主要IPベンダとも複数のIPの提供が可能となるよう開発を進めていることを明らかにした。

このほか、同氏は22nm以降の微細プロセスにも言及した。「22nmプロセスでは、第2世代のHKMGが導入され、プロセスとしてもゲートラストをさらに進化させたHigh-Kラストのプロセスが導入される予定。また、プレーナ型のほか、Fin-FETの導入も検討が進んでおり、おそらくは決定となるはず」(同)と、3次元構造のトランジスタが量産プロセスに適用される可能性が出てきたことを説明したほか、第5世代の歪み技術やCuポストの鉛フリーバンプ技術、TSV(シリコン貫通ビア)などの技術提供も予定されていることを明らかにした。

また、「Low-Rの配線材料をさらに進化させていくことで、28nm以降、ITRSが提示する配線抵抗値よりも下げることができるようになり、22nmではその成果がより高まることとなる」とより低消費電力性能と処理性能の向上の両立が可能になることを強調するが、「こうした技術を導入する結果として、コストが高くなる可能性がある」ことにも言及した。

「我々はウェハコストの上昇をプロセスの世代が進むごとに15%程度に抑えてきた。しかし、リソグラフィの変化およびFin-FETなどのトランジスタ構造の変化でそれが崩れる可能性がある。リソグラフィについては、22nmでは初期はArF液浸のダブルパターニングを導入。その後、コスト次第ではEB直描なども検討していく」とするが、次世代リソグラフィの本命であるEUVについては、「先日、EUVを吊り上げるためのカスタムクレーンの契約を行ったが、それだけで190万ユーロもした。本体は一説によれは1台あたり8,000万ドル程度とされている。これでは、製造コストが増大しすぎて、誰もカスタマは次世代プロセスを活用してくれない」と、製造コストの増大の危険性を指摘。「TSMCでは、こうした状況をなんとか打開したいと考えている。それは、パートナー企業各社との協力を進めていくことで、できることをすべて行い、最適なNGL(次世代リソグラフィ)の検討をより進めるほか、ウェハの450mm化の進展などにより、コストを抑制することを考えている」(同)と、出来る限りの努力でコスト抑制を実現していきたいとした。

すでに同社ではコスト低減の一環として300mmウェハ対応工場である「Fab12」「Fab14」の拡張を進めており、2010年末には2Fab合計でサッカーコート12面分以上のクリーンルームの広さが拡張される計画となっている。

|

|

|

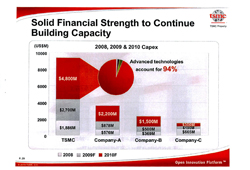

TSMCの設備投資額は、ほかのファウンドリと比べてもかなり高く、2010年には48億ドルが予定されている。結果として、先端プロセスへの素早い対応および、高い生産能力による製造コストの低減が可能になると同社では説明している |

|

「TSMCではすでに20nm以降のプロセスについての検討も開始しており、そこにコストも人員も大量に投入している。我々にはその投資に耐えうる資金がある。カスタマの生産能力を担保できる支援を行っていくことで、互いがWin-Winの関係を構築できるような関係をより築いていくことで、互いにさらなる成長を達成していければ」(同)と将来への期待を示した。