三洋電機の半導体子会社である三洋半導体は3月18日、イヤホンだけで通話が可能となる"イヤホンマイク"を実現する「イヤホンマイク用LSI」の第2世代品となる「LC70701LG」を開発、サンプル出荷を開始したことを発表した。サンプル価格は800円で、量産時は月産10万個の生産を予定している。

|

|

三洋半導体 LSI事業本部 システム事業部 IP開発部 部長の大橋秀紀 |

イヤホンマイクは、カナル型イヤホンを耳に装着、専用LSIと組み合わせることで実現される。基本的な仕組みは、「声は口から出ると思われているが、耳と喉はつながっており、非常に弱いが耳からも音として発せられている。それをイヤホンの振動板で感知し、LSIで増幅するといったもの」(同社 LSI事業本部 システム事業部 IP開発部 部長の大橋秀紀氏)としており、「イメージとしては糸電話の原理を小さくしたものに近い」(同)とする。

そのため、イヤホンマイクでは見た目上はマイクが存在せず、イヤホンのみでの使用が可能となっている。また、片耳だけで会話のやり取りが可能なため、「安全面にも配慮し、外部の音が聞こえなくなる危険性をなくした」(同)とする。

カナル型イヤホンについては、スピーカ部をマイクにもする必要があることから、「インピーダンスのバランスが重要」(同)としており、イヤホンメーカーとの共同開発が必要とする。また、推奨構造の場合、3重の遮音構造と高密度イヤーパットを組み合わせることで、イヤホン単体で雑音を1/6に低減できるという。ちなみに、カナル型イヤホンのほか、音漏れがしない密閉式ヘッドホンでもイヤホンマイクには適用でき、こちらの方がスピーカ部が大きい分、インピーダンスのバランスはゆるくなるとのこと。

LSI部は、これまで別々だったイヤホンマイクLSIとノイズキャンセルLSIをSoC化している。プロセスはアナログ・デジタル混載プロセスを採用し、従来LSIの0.25μmプロセスから0.15μmプロセスへと変更することで、アナログ部分の消費電力の抑制を実現したほか、デジタル部分の低消費電力化IPライブラリの活用により、消費電流を従来の70mA(2チップ合計)から18mAへと低減することに成功したほか、デジタル部の動作電圧を従来の1.5Vから1.1Vに引き下げることに成功している。

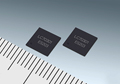

また、1チップ化によりチップ面積を2チップ合計の10mm×10mm×1.7mmから約82%、体積にすると約92%減となる6mm×6mm×0.8mmのFLGA64パッケージに収めることに成功した。なお、パッケージについては、基本はFLGAだが、顧客の要望次第では別パッケージも用意するとのことである。

さらに、音声処理のために独自の16ビットDSPコアを搭載したほか、音声変換のためのΔΣ方式の16ビットA/DコンバータおよびD/Aコンバータを搭載。これらのコンバータおよびマイクアンプの特性向上を図ったことにより、前世代LSI比でS/N比を約10dB向上させることに成功した。加えて、ソフトウェア性能の向上およびアルゴリズムの改良により、クリアな音質を実現している。

これらの技術を組み合わせることで、雑音を1/10に低減することが可能であり、イヤホン側の工夫と合わせることで、最大で雑音を1/60にまで低減することが可能としている。

主な対象アプリケーションはBlurtoothヘッドセットを想定しており、すでに3月12日にSMKが発表したマイクレスBluetoothヘッドセット「FX 7009」に先行して搭載されているという。

なお、2010年には第3世代となる「LC7070X」の開発を終える計画だが、「基本的な考え方はさらなる低消費電力化と高音質化、そして小型化」(同)としており、「消費電流は現行の18mAから10mA以下まで引き下げたい」(同)とする。そのためにはプロセスの微細化なども視野に入れるが、アナログ・デジタル混載での微細化は、「130nmもしくは110nm程度までなら行けるかもしれないが、90nmではアナログ部分のS/N比がとれるかどうかなどの問題があり、今後の検討が必要となる」(同)としている。