Xilinxは10月27日、台湾において同社の次世代製品である28nmプロセスを使ったVirtex-7のハイエンドモデルに採用される、Stacked Silicon Interconnectの技術を発表した。これに先立ち前日の10月26日、日本法人であるザイリンクスのオフィスにて本社のIvo Bolsens氏(Photo01)およびDavid Myron氏(Photo02)を招いて記者説明会を開催した。

基本的な話は、FPGAでもマルチチップ化の方向性が見えてきており、これを実現するために直接従来のパッケージ上に実装するのではなく、Silicon Interconnectを利用したということである(Photo03)。この動機は、より高速・大容量・高性能のFPGAを引き続き顧客が求めているということにある(Photo04)。とは言っても、既にFPGAはかなり大型化しており、Yieldが低い=高価格かつ入手性に難がある、という問題がある(Photo05)。

そこで対応として従来は、複数のFPGAをPCB上に実装するとか、まれにFPGAをダイで購入してMCM上に実装するといったケースもあったが、こちらはFPGA同士の接続にかなりのI/Oピンを費やすことになり、またこれに伴うレイテンシ増加や消費電力が問題になることになる(Photo06,07)。

|

|

|

Photo06:まぁ汎用I/Oピンで通信を行うのだから、これは致し方ない成約ではある。右下の図はPhoto07参照 |

Photo07:こちらは実際のプレゼンテーション(Photo06は日本語翻訳済資料だが、図の説明が潰れてしまっている)。要するにGate数の増加にBumpやパッケージのPinの増加が追いついていないのが最大の問題という訳だ |

こうした問題に対する解が、今回発表されたStacked Silicon Interconnectである。FPGAのダイを複数横に並べ、そこにStacked Silicon Interconnectを接続することで、横方向に拡張する形となる(Photo08,09)。実際にはFPGAのダイはまずMicroBump経由でStacked Silicon Interconnectに接続され、この中でダイ間の相互接続が行われる。このStacked Silicon InterconnectはTSMCの65nm low-kプロセスを用いて製造される。更にここからTSV経由でC4 Bumpと接続され、更にパッケージと接続されるというものだ(Photo10)。

言ってみれば通常のMCMに、もう一層Silicon Interconnectを挟んだ形になる。何故これが必要か、に関してBolsens氏は

- Microbumpを使う事で、従来のMCMよりも多数のInterconenctを利用できるようになる。

- (65nmプロセスの)Silicon Interconnectにより、配線密度を大幅に上げることが可能になった。

- (Low-K材料による)Silicon Interconnectを使う事で、MCMなどに比べて圧倒的に少ない電力で高速に信号伝達が可能になり、省電力に加えて高信頼性も確保できる。

という3つの利点を挙げた。実際これを使う事で、FPGA同士の接続ピン数が大幅に増え、しかも遥かに高効率であることを強調した(Photo11)

|

|

Photo11:例えばStacked Silicon Interconnectを使ってFPGA同士を11,000本で接続し、200MHzで通信を行った場合の消費電力は0.5W以下であるとする。同じ事を従来のSerDes経由で行うと、1300pinを1.6GHzで通信する必要があり、この場合の消費電力は50Wを超えるそうだ |

今回のStacked Silicon Interconnectは、Bolsens氏によれば「確実に実現できることを重視する」ために、あえてアクティブ部品は一切含まず、純粋に配線層だけで構成されているとか。ただ将来的には、例えば電力管理用のトランジスタスイッチといったアクティブ部品が含まれることは否定しなかった。

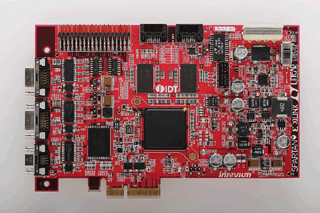

これによるユーザーメリットは?ということであるが、まず従来は(ダイサイズの制限もあって)実現できなかった巨大なFPGAが利用できるようになるということである(Photo12)。またこのマルチチップFPGAは、1つのプロジェクトとして開発が出来る(Photo13)事もデモを交えて紹介された。量産への移行も順調で(Photo14)既に試作品は第3世代まで完成し(Photo15~18)、ほぼ開発は完了しているという。ちなみに信頼性に関しては、むしろStacked Silicon Interconnectを介した方が効果的であったとの事である(Photo19)。

|

|

|

Photo12:これはハイエンド製品同士での比較であるが、概ね従来製品に比べて3倍のロジックセルを実現できる、としている |

Photo13:ISE 13.1からはこのStacked Silicon Interconnectを利用したマルチチップFPGAを、1つの巨大なFPGAとして扱える様になったとしており、実際にビデオ上で複数のFPGAダイに跨って配線を行う例が示された |

|

|

|

Photo14:Bolsens氏はこの技術を5年に渡って開発を行ってきたとしており、2008年からは実際に3世代のプロセスを使った試作品で様々な検証を行ってきたという。既に製品のエンジニアリングサンプルはISE 13.1のβ版とあわせて一部の顧客の元に渡って、実際に開発に使われているとの事だ |

Photo15:第3世代の試作品のパッケージ。ダイに細かく3本の切れ目が入っているのが判る |

|

|

|

Photo16:パッケージ裏面は通常のBGA |

Photo17:ダイ+Stacked Silicon Interconnect。ダイの周囲にはみ出しているのがStacked Silicon Interconnectである。厚さは極めて薄かった |

なお今回のStacked Silicon Interconnectの主要パートはTSMCとAmkorが担っている形であるが、最終的なパッケージの責任をXilinxが行う事も、従来のMCMや複数のFPGAを顧客の責任で接続するよりも有利な点である、としている(Photo20)。

ちなみにTSMCもこうしたSilicon Interposerの構造に強い興味を持っており、将来的には3Dやアナログ部品のInterposerへの埋め込みといったオプションを提供してゆく考えを示しており、今回Xilinxと共同で提供できることを嬉しく思う、というメッセージを述べた(Photo21)。

|

|

Photo21:このスライドのみ、TSMCのものである。将来的にはTSVなどを使った3D構造が主流になるが、まずはSilicon InterposerによりMCMの高性能化・高密度化を狙うのが第一のステップという事らしい |

このStacked Silicon Interconnectを最初に利用するのは、2011年後半に投入される「Virtex-7 2000T」で、これは200万ロジックセルと36個の10.3Gbpsトランシーバを内蔵したものになる。Myron氏によれば、他に4つの(Stacked Silicon Interconnectを利用した)製品のバリエーションがあるそうで、トータルで5つの製品がマルチチップFPGAとして登場することになるようだ。もっとも28nmプロセスを使う製品そのものはもう少し早く(2011年第1四半期)登場することも改めて確認された。