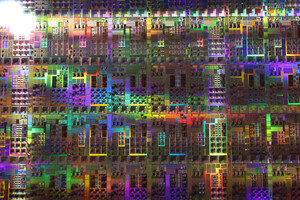

高性能なシステムを高速に運用したい、またはしなければならないという背景から、その用途を満たす方法のひとつとして、いまFPGAが注目されている。『ソフトウェア・エンジニアのためのFPGA入門』と題し、これまでFPGAに触れてこなかった方々へFPGAを紹介する当企画。今回はFPGAの仕組みと構造を紹介する前段階として、一般的なRAMの仕組みを解説したい。

メモリの仕組み

FPGAを構成する主要部分であるLUTはメモリでできている。このため、FPGAを使いこなす一歩として、まず一般的なメモリの仕組みについて知っておいてもらいたい。

-

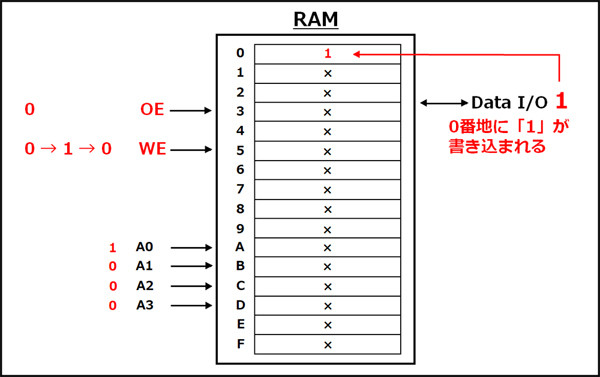

図1 メモリの仕組み、ここでは16bit RAM(Random Access Memory)を例とする

図1に1bitデータ幅、容量16bitのSRAMの構成イメージを示す。データ幅が1bitなので、データの入出力端子は1本である。ほかに16bitのメモリ空間を示す4bitのアドレス入力端子と、出力および書き込み制御を行う入力端子がそれぞれ1本ある。OE (Output Enable) 入力端子が1のときはData I/Oからアドレス入力端子で指定されたアドレスのデータが出力される。OEが0のときはData I/Oは入力状態となる。従って、データの書き込みを行う場合はOEを0にする必要がある。WE (Write Enable)はデータの書き込み指示を行う端子で、通常は0にしておく。OEが0のときにData I/Oから該当のデータを入力した状態でWEを1にして0に戻すと、指定のアドレスにデータが書き込まれる。

この手順について、アドレス0番地に1を、それ以外のアドレスに0を書き込む例で説明する。まず0番地に1を書き込むには、図2のようにアドレスA0~A3に0000を入力する。同時にOEとWEも0とし、Data I/Oに1を入力する。この状態のまま、WEのみ0から1にして、さらに0に戻す。次にこの状態から、1番地にデータを書き込むので、図3に示すようにアドレスを0001とする。その他は先程と同じ手順となる。これをF番地までの全てのアドレスに対して行う(図4)。

次に書き込まれたデータの読み出しは図5に示す通り、読み出したいアドレスを指定してOEを1にするだけである。以上がSRAMの基本動作となる。FPGAはこのSRAMを用いて論理回路を実現している。

-

図2 メモリの0番地に1を書き込む

-

図3 メモリの1番地に0を書き込む

-

図4 メモリのF番地に0を書き込む

-

図5 メモリの0番地に書かれたデータを読み出す

ここまで、FPGAの演算処理の中心であるLUTに使用されている、一般的なRAMの動作について解説した。次回はこのRAMを使用してLUTが実現される仕組み、そこからいよいよ、本企画のメインテーマとなるFPGA全体の構造と仕組みについて紹介する。

著者プロフィール:すすたわり

株式会社SUSUBOX代表取締役。慶應義塾大学 特任准教授。元FPGA-CAFE店長。主な著書に「回路図で学べるFPGA入門 回路図は読める人のためのHDLガイド」(秀和システム)がある。

[PR]提供:アヴネット