Hot Chips 27においてカリフォルニア大学バークレイ(U.C. Berkeley:UCB)校のYunsup Lee氏がキャパシタを使うDC-DCコンバータを搭載するRISC-Vベクタプロセサについて発表を行った。

RISC-V(リスク ファイブ)はUCBのKrste Asanovic教授が主導するプロジェクトで単純で効率の良いアーキテクチャを作ろうという研究を行っている。RISC-Vの命令セットのドキュメントは、Krste Asanovic教授とDavid Patterson教授によって書かれているが、Patterson教授はヘネパタ本で有名な先生であり、Asanovic教授は、現在のUCBのコンピュータアーキテクチャ研究をリードする先生である。

エネルギー効率改善を目指すRavenプロジェクト

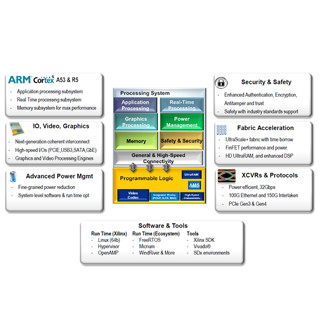

「Raven」と呼ぶ今回発表のプロジェクトは、現在、最大の問題となっているプロセサのエネルギー効率を改善することを目的としている。エネルギー効率を改善するには、動作状態に応じて電源電圧とクロック周波数を調整するDVFS(Dynamic Voltage Frequency scaling)が有効な手段である。

しかし、オフチップの安定化電源では多くの出力を出すのは困難で、すべてのブロックにきめ細かく最適の電圧を供給することができない。また、チップ外に電源回路の部品が必要でありコストアップになる、電源電圧を変えるのが遅いなどの問題がある。これらの問題は、安定化電源回路をCPUチップに集積してしまえば、ほとんど解決する。

この考えは正しく、IntelはHaswell CPUに、インダクタンスを使う安定化電源回路「FIVR」を搭載した。しかし、後継のSkylakeでは搭載を辞めてしまった。その理由は公表されていないが、どうも、設計がHaswellを開発した米国のヒルスボロのチームから、Skylakeではイスラエルのハイファのチームに移り、イスラエルチームはFIVRを採用しなかったということではないかと思われる。なお、Haswellでは、安定化電源回路はチップに集積されているが、インダクタンスはパッケージ基板の配線を利用して作っている。

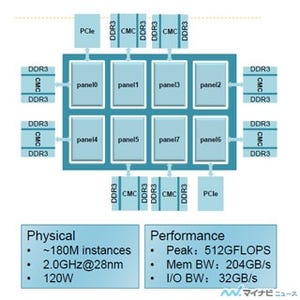

Ravenプロジェクトでは、細かい単位でのDVFS制御を高い変換効率で実現し、かつ、すべての回路をチップ上に集積して、必要なチップ面積も少なくて済むという設計を目標としている。

スイッチドキャパシタ方式のDC-DCコンバータを搭載

Ravenでは、電源電圧の変換方法として、スイッチドキャパシタという方式を使っている。キャパシタの方がインダクタより、チップへの集積が容易であることがその理由と考えられる。

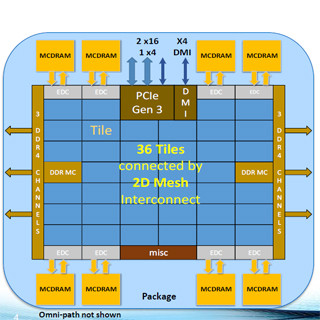

次の図の左下のように、1Vの電源をキャパシタを通してチップに供給し、チップに電流が流れると、キャパシタに電荷が溜まってくる。そして、キャパシタの電圧が0.6Vになると、チップに掛かっている電源は0.4V程度となる。この状態で左上のように、キャパシタの+/-を反転してL側をグランドに繋ぐと、キャパシタの0.6Vの電圧がチップに掛かることになる。

この状態でチップが動作を続けると電源電流が流れ、キャパシタに溜まっている電荷が徐々に減り、0.4Vまで下がる。この時、キャパシタの方向を反転して、1Vの電源を繋ぐとチップの電源電圧は0.6Vになる。その後、チップに電流が流れるにつれて電源電圧は下がって行き0.4Vまで下がったところで左下の状態となる。このループを繰り返すと、1Vの電源を供給し、チップには0.4~0.6Vの電圧を供給するDC-DCコンバータとなる。

このような動作を行わせるためには、キャパシタの両端に2個ずつのスイッチをつけたユニットセルを多数個造る。大きなキャパシタを作るより、一定サイズの小さなキャパシタを多数作った方が配置の自由度が大きくレイアウトが楽である。

(次回は9月19日に掲載します)