シミュレーション性能を強化したCM-2

Hillis氏は、人工知能ではなく、数値シミュレーションを行うマシンを作ることには前向きでなかったようであるが、CM-1は7システムしか売れずビジネスにならないので、スパコンの主流である数値シミュレーションができるCM-2を開発することになった。

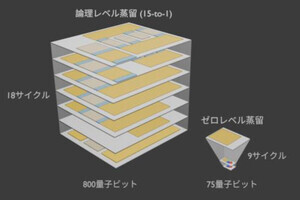

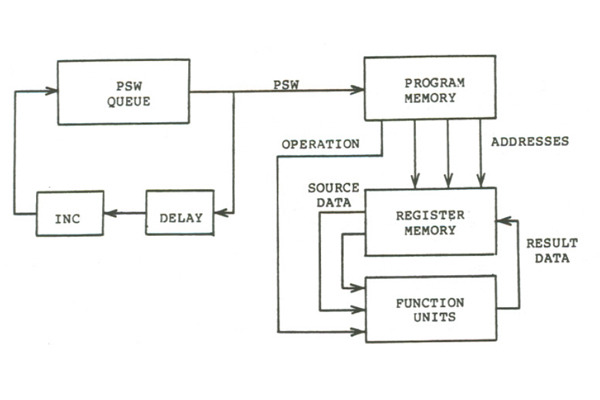

次の図に示すように、CM-2は2つの16プロセサチップの先に、Sprintチップを付け、そこからWeitek社製の浮動小数点演算器を接続している。さらに、各プロセサに接続するメモリがCM-1では4096bitであったが、CM-2ではこれを64Kbitに拡張し、サポートできる仮想CPUの数を16倍に増強している。その結果、64KプロセサのCM-2は14.34GFlopsの浮動小数点演算性能と8GBのメインメモリを持つマシンとなった。

また、CM-1のクロック周波数は4MHzであったが、CM-2では7MHzにクロックアップしており、その分、性能が向上している。

このCM-2は1986年に発表された。なお、CM-2ではベクタユニットが追加されているので、1キューブに収容できるプロセサノード数が減り16Kノードのシステムには8キューブが必要になったと考えられる。

-

図3.10 CM-2のノードのブロック図。Sprintチップを経由して、32個のプロセサに対して1個の浮動小数点演算器を接続したCM-2のSprintノード (出典:http://www.umiacs.umd.edu/research/EXPAR/papers/3123/node1.html)

また、TMCはCM-2の高速化版である「CM-200」も開発した。CM-200はCM-2のCPUクロックを10MHzに高速化したマシンである。なお、CM-2とCM-200の浮動小数点演算部の性能は同じで、浮動小数点演算部のクロックは上がっていないようである。次の図3.11はCM-200の外観で、8個のキューブで16Kプロセサを収容している。なお、前面に見える赤いしみのようなものはそれぞれがプロセサに対応する赤いLEDで、各プロセサの動作状態がモニタできるようになっている。

なお、CM-1とCM-2の筐体などのデザインはスタンフォード大でプロダクトデザインを学び、MITで機械工学の修士号を取った日系アメリカ人のTamiko Thiel氏が担当したものである。

-

図3.11 8個のキューブからなる16KプロセサのCM-200と円弧状のキャビネットのData Vaultストレージ (出典:https://social.shorthand.com/EPCCsocial/nyAcT3A0Pf/cm-200-connection-machine)

CM-1、CM-2、CM-200は、全プロセサに並列に命令を送ったり、プロセサ間の同期を行ったりするControl Networkとプロセサノード間、プロセサノードとメモリ間などでデータを送受するデータネットワークを持っている。12次元のハイパーキューブという接続リンク数の多いネットワークであるので、たくさんのケーブル接続が必要であり、次の写真に見られるように、プリント板のバックパネル側には大量のリボンケーブルが接続されてい

-

図3.12 CM-200のバックプレーン側の写真。白いリボンケーブルはノード間を接続しているネットワーク (出典:http://www.corestore.org/cm200.htm)

(次回は11月29日に掲載します)