AMD CPU

Zen 4及びZen 4cベースの製品をほぼ全てロードマップ通りにリリース出来たのが2023年であった。2022年6月に示されたロードマップによれば、Zen 4世代はZen 4とZen 4+3D V-Cache、それとZen 4cがリリースされる予定で、この全てが既に出荷開始している。またZen 4製品は基本的にTSMC N5を使うが、Ryzen 7040シリーズやRyzen Pro 7040シリーズ、それに2023年12月に発表されたRyzen 8040シリーズはTSMC N4での製造となっている。といってもTSMCのN4はトランジスタ密度が若干(138.2MTr/平方mm→143.7MTr/平方mmなので3.9%程度)向上している程度で、配線密度などは変わりがない。N4PとかN4Xであればまた性能も向上するのだが、今のところN4Pに移行するよりも、N3Eへの移行した方が賢明だと考えているようだ。

さてそのZen 5であるが、これは結構な内部変更になると見られている。結果的にAMDもTick-Tock戦略を実行している格好になるが、いわゆる旧来のTick(プロセス刷新)とTock(アーキテクチャ刷新)に従えばZen 3→Zen 4ではマイクロアーキテクチャは大きく変わらず、その代わりプロセスは7nm→5nmに刷新されたので、これはTick扱いになる。これに対してZen 5はマイクロアーキテクチャレベルで色々手が入ったものになる、と予想されている。ただそれに加えてプロセスもTSMC N3Eに移行するので、Tick+Tochという形になると見た方が正確なのかもしれない。

さて、そのZen 5のマイクロアーキテクチャ(Nirvanaというコード名だそうだ)であるが、Zen 4からかなり強化された重厚なものらしい。Zen 4のマイクロアーキテクチャはこちらが判りやすいが、Zen 5では

- 8 wide dispatch/rename(Zen 4は6)

- 6 ALU(Zen 4は4)

- 4 Load/2 Store(Zen 4は合計で4)

という事になっている。またはっきりしないが、FPUはどうも512bit幅に拡張されたらしい。Decode段の性能は不明だが、ここまでDispatchを増やしている以上、最低でも5 x86命令のDecodeが可能で、ひょっとすると6かもしれない。L1 I-Cacheは32KBで据え置きだが、L1 D-Cacheは48KBに拡張されている。性能の方は不明だが、Single Thread性能(≠IPC)が最大30%向上、という数字もあるらしい。他にも分岐予測メカニズムの強化なども上がっており、Tickに相応しくかなり手が入ったものになっている模様だ。実際ALUの数だけなら、Alder Lakeに搭載されたGolden Coveを上回る規模になっている。

ただ今一つはっきりしないのが、Mobile向けの構成である。2023年12月に発表されたHawk PointことRyzen 8040は、いわばPhoenix Point Refreshとでもいうべき中継ぎであり、本来のPhoenix Pointの後継はこちらにも出てくるStrix Pointである。ただこのStrix PointはMobile向けのAPUで、しかも恐らくMonolithic Dieの構造になりそうだ。そこに16coreブチ込むのか? というとかなり怪しい。とはいえZen 4ベースという事も無く、Zen 5にはなるようで、どうもZen 5世代のCCXはかなりフレキシビリティがありそうな気配がある。

というのは、Strix PointはZen 5コアにRDNA 3(3.5、という話もあるが不明)、それとXDNA 2のNPUを組み合わせた構成になるが、その先にはZen 5+Zen 5cというHybrid構成もあり得る(少なくともそういう計画はあるらしい。本当にそういう製品が出て来るか、はまた別の話だが)そうで、それをいちいちCCXを分けていると無駄にダイサイズが大きくなる。どうも最小構成は4coreで、8/12/16coreまでスケール可能で、かつZen 5とZen 5cの両方を利用できる仕組み、という事になっている様にしか筆者には考えられない。まぁそういう形にCCXを構築する事そのものは不可能ではないだろう。(Strix Point自体がZen 5+Zen 5cになる、という話もあるのだが、正直かなり怪しいと考えて居る)。このStrix Pointは今年前半中の投入を目指している様なので、プロセスはTSMC N4でという事になるだろう。

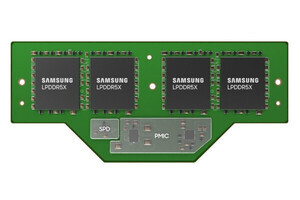

では従来のRyzenとかEPYCに使われている方は? というと、これはN3Eを利用しての生産となり、恐らく第3四半期末~第4四半期の投入になると思われる。こちらはDieあたり16coreだから、Desktop Ryzenは32coreまでとなり、EPYCはGenoaと同じプラットフォームで192coreが実現する事になる筈だが、実はTurinは128core止まり(つまり最大でも8CCD)で、Zen 5cを積んだBergamo Next(Turin Denseという言い方もあるそうだ)で192coreを実現という報道もある。ただまぁGranite Rapidsが132coreだそうだから、128coreあれば十分競合できる構成である。プラットフォームそのものは変更が無く、DesktopはAM5のままだし、ServerはGenoaと共通のSocket SP5を利用した形となる。気になるのはメモリ帯域だが、Granite Rapids同様にTurinもMR-DIMMをサポートする事になると見られる。なのでDDR5-8800相当ということでGenoaのDDR5-4800の倍にはならないもののの83%増しということで、一応コアあたりのメモリ帯域はGenoa世代より4割弱増える計算になる。あとはIPCの改良や大容量化されたと思われるL2でカバーというあたりだろう。

ここで気になるのは、最終的にL2/L3がどのくらいの容量になるかということだ。現在聞こえてきている話では、L2は2MBないし3MBに増量され、L3は32MB/CCXで据え置きらしい。この2つある、というのはCCDが2種類あるという風には考えにくい。可能性的に言えば、Zen 5が3MBでZen 5cが2MBというあたりか。一方のL3、内部的には32MBのUnifiedではなく、16MB×2になっているという話が伝わってきている。理由は? というと、Unified L3に16個のコアがぶら下がる形になると、L3 AccessのLatencyが大きくなりすぎてしまうため、ということらしい。なので8コアづつ16MBのL3に接続する形で、L3同士はInfinity Fabricで接続(ということは、つまりCCDから一度IOD経由で繋がる形)に戻るようだ。これ、中身で言えばCCXが16コアに対応、というよりはAMDがBergamoで実装した「一つのダイの中に2つのCCXがあり、それぞれ8core/32MB」の構成をちょっといじり、8core/16MBに変更したCCXを2つ実装した、という方が近いように思える。

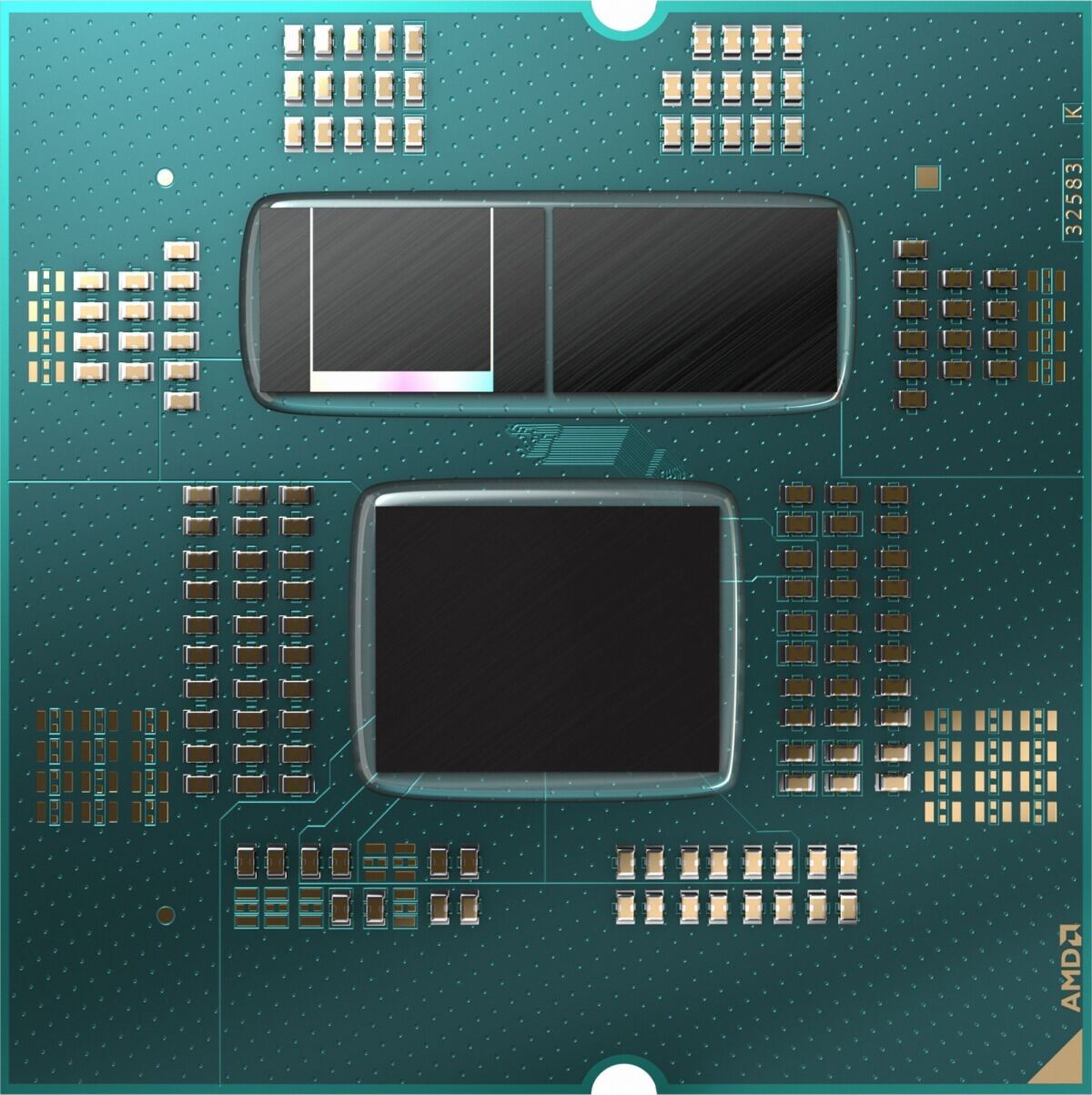

L3が半減した理由はダイサイズ削減だろう。TSMCのN5→N3EだとChip Densityは最大1.3倍程度になるとされる。それでいてコア数は倍だから、ロジック領域は53.8%ほど面積が増えることになる。ちょっとZen 4世代に戻って、Ryzen 9 7950X3Dの3Dレンダリングイメージ(Photo07)を見ると、左側のダイのうち3D V-Cacheの面積はダイ全体の55.4%ほど。ここはそのままL3の面積になるから、それ以外は44.6%程になる計算だ。で、この44.6%の部分がプロセス微細化+コア数増加で53.8%面積が増えたとすると、Zen 5 CCDの面積はZen 4 CCDの24%増し程になる計算だ。Zen 4 CCDの面積が概ね71平方mmとされるから、Zen 5 CCDの面積は88平方mm程になると予測される。ちなみにこれはL2の大容量化は考慮していないラフな計算なので、実際はもう少し大型化し、90平方mm台になりそうだ。仮にここでL3を大容量化したとすると、Zen 5 CCDの面積は130平方mm台に達する計算になる。昨日のプロセス編でも触れた様に、3nmのWafer製造コストは5nmの1.5倍であり、更に面積が倍近くなったらZen 5 CCDの原価はZen 4 CCDの3倍に達する計算になる。流石にAMDとしてはこれは許容できないだろう(と言うかL3を32MBに据え置いても、Zen 5 CCDの原価はZen 4 CCDの原価の倍近くなる)。L3を増強しなかったのはある意味苦渋の選択だったのだろう、という気がする。ただL3に関しては3D V-Cacheを使うという逃げ道があるので、これでよしとしたのだろうとは思うが。

なお、2024年に投入されるDesktopのRyzenに関しては、GPUはRDNA3ベースながらEU数はかなり抑えたものになるだろう。IODは引き続き6nmでの製造と目されており、またDesktop向けはメモリ帯域も精々DDR5-6400をサポートする程度だから、GPUを強化してもそれほど描画性能は上がらない。ここでの大幅な性能向上は期待できないだろう。