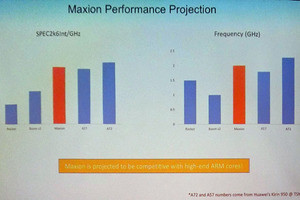

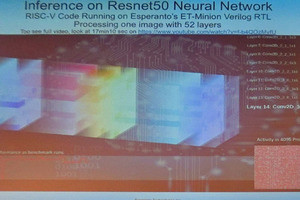

ET-SoC-1はTSMCの7nmプロセスで製造され、1チップに1088個の電力効率の高いコアを搭載している。ET-Minionコアは64bitのRISC-Vアーキテクチャのプロセサで、各コアにベクトル/テンソル演算器を備えている。Minionコアはインオーダ実行であるが、Maxionコアはアウトオブオーダ実行を行う高性能コアである。Maxionコアはチップには4個搭載されている。

さらに、オンチップで160MB以上のSRAMを搭載している。I/OはPCIe Gen4を8チャネル持ち、その他の標準的I/Oインタフェースも装備している。

そして、Esperantoの低消費電力アーキテクチャと低電力回路技術で、100~200TOPSの演算性能と20Wという低消費電力を実現しているのが特徴である。

Esperantoの創立者のDavid Ditzel氏は、x86互換の低電力CPU「Crusoe」を作った人で、低電力プロセサの開発には長い経験をもっている。その経験から、簡素で電力消費の少ないRISC-Vアーキテクチャを採用し、CPUの演算器などのロジック部分は0.4~0.5Vの電源電圧で動作する回路設計を行って作り上げたのがET-SoC-1である。

リコメンデーションの処理には100~1000TOPSのピーク演算性能が必要になる。同時に、消費電力は75~120Wに抑え、空冷で冷却できるように作るべきである。int8の演算性能が最重要で、fp16とfp32も演算できる必要がある。

そして、アクセラレータボードには~100GB程度のメモリを必要とし、チップ上には~100MBのメモリが必要という。

そして、密行列の演算も疎行列の演算も高い性能が得られることが重要であるという。密行列の場合はGoogle TPUのようなシストリックアレイ演算器でも良いが、疎行列の場合はET-SoC-1のようにマルチスレッドで、多くの不連続のメモリブロックに並列にアクセスできるアーキテクチャの効率が良い。

他のMLアクセラレータチップは巨大なチップに全体を入れているが、このやり方ではメモリバンド幅が増やせない。Esperantoのアプローチは低電力のプロセサチップを複数個(ET-SoC-1の場合は6個)使用する。複数チップを使用すればメモリバンド幅を増やすことができ、特に、コアごとに独立の番地をアクセスできるので疎行列のアクセスを高い性能で行うことができる。

そして、Esperantoの場合は、1000以上のスレッドが使えるので、多くのアドレスを並列にアクセスすることができる。

プロセサの消費電力はCdynamic×Voltage2×Frequency+Leakageで表される。24コアで165Wのx86の場合はクロック3GHz、電源電圧0.85VでCdynamicは2.2nFという計算になる。これに対して10mWのMinionコアの場合はコアの消費電力は0.01W、クロックは1GHz、電源電圧は0.425VでCdynamicは0.04nFという計算になる。

ただし、電源電圧を半分の0.425Vに下げることは容易ではなく、SRAMではデータ保持力が低下して特に難しい。また、MinionはコンパクトなコアであるがCdynamicを1/58に減らすのも極めて難しい課題である。

そこで、120Wの消費電力で、どのようなチップにすれば良いかを検討した。図8のグラフは縦軸がエネルギー効率で、横軸は電源電圧である。0.9Vの電源電圧では275Wの消費電力となるが、トランジスタの効率が最も高い0.3Vでは(クロック周波数を別とすれば)8.5Wで実現できる。1チップに118Wを使うというやり方もあるが、20Wを6チップというやり方をすればリコメンデーション性能を4倍にできる。このため、Esperantoは20Wチップ6個という設計ポイントを選択した。

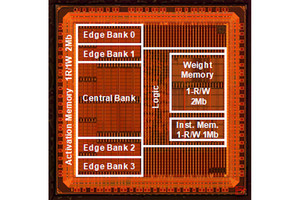

図9はET-Minionコアのブロック図である。アーキテクチャおよび回路的に低電圧動作に最適化した設計となっており、演算器は512bit幅のint8整数ベクトル、256bit幅のfp16/fp32浮動小数点ベクトル、新設のマルチサイクルのテンソルベクトル処理機構を持っている。

個々のET-Minionコアはint8ではピーク128GOPS/GHzの演算性能を持っている。

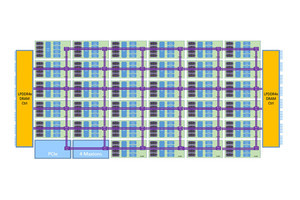

図10に示すように、32個のMinionコアが狭い領域に隣接してレイアウトされている。この32コアで1次命令キャッシュを共用しており、同じ命令列を使っている場合は、1つのコアが命令アクセスするエネルギーで、多くの場合、その他のコアの命令を含むキャッシュラインアクセスができてしまい効率が良い。また、データアクセスもべクトルの多くの要素を高い効率で利用でき、効率が良い。このため、8個のMinionコアをご近所という扱いにしている。この隣接データをついでにアクセスしてしまうという方法で、消費電力を減らすのがEsperantoの省電力の秘策である。そしてEsperantoのプロセサではSend-to-Neighbor、Receive-from-Neighborという命令を新設して、より効率を引き上げている。

-

図10:8個のMinionコアを単位として近所にレイアウトして、1次命令キャッシュを共用している。8コアが同じ命令を使ったり、同じキャッシュラインにアクセスしたりするケースが多く、バンド幅やエネルギーの点で効率が良い

図11は32個のET-Minionコアを纏めたMinion Shireの図である。図10に示した8個のMinionを纏めたご近所が4つ存在し、それが4×4のクロスバの左側に繋がっている。そして4×4のクロスバの右側にはBank0~Bank3の1MBのメモリスライスが繋がっている。

そして、Shireの図の右端にMesh Stopがあり、ここからメッシュネットワークを経由して他のMinionコアにつながる。また、メモリやI/Oのトラフィックもメッシュネットワークを通って接続されている。

多数のコアがあり多数のスレッドがあるので、それらの同期は重要である。ET-SoC-1はメッシュネットワークを使ってアトミック命令やバリア命令などを高速に実行できるようになっている。

図11で興味深いのはクロスバとSRAMのバンクのところがNormal Voltageと書かれている点である。このSRAMはビット数が多いので低電源電圧で動作するSRAMセルではなく、密度優先で6TRセルを使っているようである。そのため、Minionコアで使っている0.4V程度の低い電源電圧ではなく、0.7~0.8V程度のNormal Voltageを使っていると考えられる。なお、クロスバは低電圧でも動作しそうであるが、レイアウト上SRAMにくっついているのでNormal Voltageになっているとのことである。

-

図11:8個のET-Minionコアを4つまとめ、44の1MB SRAMを4×4クロスバで接続したMinion Shire。Minion ShireからMesh Stopを経由して他のMinion Shireに接続されている

図12はMinion ShireとMesh Stopの接続部分を拡大した図である。Mesh Networkは2次元のメッシュであり、Mesh Stop間の接続は単方向×2の伝送路が設けられている。

次の図13はET-SoC-1の全体のブロック図で、図1に掲げたものと同じ図であるが、復習の意味で、34個のMinion-Shire、8個のMemory-Shire、Maxion-Shire、PCI-Shireを再掲している。

図14はET-SoC-1のチップ外インタフェースをまとめた図である。8bitのPCIe Gen4はrootにもendpointにも使えるポートである。次は256bit幅のLPDDR4xポートで、137GB/sのバンド幅を持ち、このポートはECCをサポートしている。

そして、ET-SoC-1はセキュアブートやシステムマネジメントを行うサービスプロセサを持っており、サービスプロセサの接続ポートが設けられている。当然であるが、ET-SoC-1はSMBusやシリアルのI2C/SPI/UAR、GPIO、Flashなどの標準の外部接続ポートも持っている。

次の図15は6個のET-SoC-1チップを搭載する巨大な疎行列を扱うリコメンデーション処理用ボードの推奨構成を示す図で、6個のET-SoC-1を搭載し24個のLPDDR4メモリが接続されているので、メモリ接続は1536bit幅となり、822GB/sのメモリバンド幅を持っている。

Minionコアの総数は6528個で、960MBのオンチップSRAMを持っている。

図15の6チップ搭載ボードの写真が図16である。OCP(Open Compute Project)の標準のGlacier Point v2ボードに表裏で合計6枚のET-SoC-1を搭載したM.2ボードを載せている。これを1GHzのクロックで動作させた場合、ピーク性能は800TOPSを超える。しかし、消費電力は120Wと、GPUや専用アクセラレータに比べて小さい電力で済む。

図17は図16のGlacier Point v2ボードをYosemite v2スレッドに2枚搭載し、4台のYosemite v2を4台Cubbyに入れ、8台のCubbyをラックに収容する。これで1台のラックには384個のET-SoC-1チップが収容されている。OCPラックの設置面積は30平方フィートで、1つのデータセンターには4K -20Kラックが設置できるので、100万個以上のET-Minionコアを収容できる。

-

図17:ET-SoC-1を使うデータセンターの実装階層。(1)Glacier Point v2 Card、(2)Yosemite v2 Sled、(3)Yosemite v2 Cubby、(4)ラック、(5)データセンター

ソフトウェアはC++、Pytorchなどで書かれたモデルをGLOWやTVMなどのツールで処理してET RISC-Vのコードを生成する。これにET-RuntimeやET-PCIe Driverなどを結合して実行コードを作る。