既報の通り米Intelは米国時間の6月18日、Cooper Lakeベースの第3世代Xeon Scalable Processor(Xeon SP)の他、Optane Memory 200シリーズや新しい3D NAND SSD、それとAIをターゲットにしたStratix 10 NX FPGAなどを発表したので、これらについてもう少し説明を行いたい。

第3世代Xeon Scalable

Cooper Lakeのコード名が初めて登場したのは2018年8月に開催されたData-Centric Innovation Summitでのこと。この際の説明では、Cooper LakeはCascade Lakeの後継として2019年中に投入される筈で、このCooper LakeのプラットフォームがそのままIce Lakeベースと互換性を持つという話であった。ところがご存じの通り、Cascade Lakeそのものが2019年にずれ込んでおり、昨年9月の説明ではCooper Lakeもそのまま2020年にずれた格好になっている。

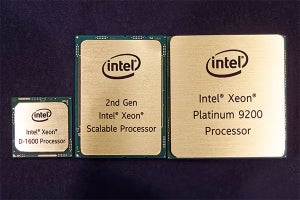

さてそのCooper Leke、現時点では表1に示すように11製品のSKUが発表されている。実は2019年8月におけるIntelの発表では、ソケットあたり56コア/112スレッドの製品も投入する旨が予告されていたが、これはちょっと後送りになるようだ。

| ■表1 | |||||

| Model | Core/ Thread数 |

Clock(GHz) 定格/Turbo |

キャッシュ(MB) | Socket数 | TDP(W) |

|---|---|---|---|---|---|

| Xeon Platinum 8380HL | 28/56 | 2.90/4.30 | 38.50 | 4/8 | 250 |

| Xeon Platinum 8380H | 28/56 | 2.90/4.30 | 38.50 | 4/8 | 250 |

| Xeon Platinum 8376HL | 28/56 | 2.60/4.30 | 38.50 | 4/8 | 205 |

| Xeon Platinum 8376H | 28/56 | 2.60/4.30 | 38.50 | 4/8 | 205 |

| Xeon Platinum 8354H | 18/36 | 3.10/4.30 | 24.75 | 4/8 | 205 |

| Xeon Platinum 8353H | 18/36 | 2.50/3.80 | 24.75 | 4/8 | 150 |

| Xeon Gold 6348H | 24/48 | 2.30/4.20 | 33.00 | 4 | 165 |

| Xeon Gold 6328HL | 16/32 | 2.80/4.30 | 22.00 | 4 | 165 |

| Xeon Gold 6328H | 16/32 | 2.80/4.30 | 22.00 | 4 | 165 |

| Xeon Gold 5320H | 20/40 | 2.40/4.20 | 27.50 | 4 | 150 |

| Xeon Gold 5318H | 18/36 | 2.50/3.80 | 24.75 | 4 | 150 |

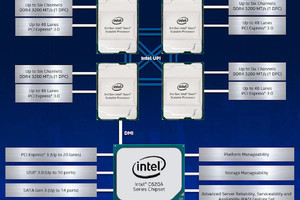

ちなみに共通するスペックとしては

- パッケージは新しいSocket P+(FCLGA4189)で、サイズは77.5×56.5mm

- Memoryは6chでRDIMM(ないしPersistent Memory)のみのサポート

- UPI Linkは全製品とも6本

- PCI ExpressはGen3×48Lane

といったあたりである。

さて先の記事にもあったが、今回Cooper Lakeは4Socketないし8Socketのみの対応である。それもあって投入されたのはXeon PlatinumとXeon Goldのみで、Xeon Goldが4Socketのみになる。それはともかくとして、一番少ない製品でも18コア/36スレッドというあたり、どうもCooper Lakeに関してはHCC(High Core Count)のダイしか存在しない模様だ。実はCooper Lake世代に関しては特定の顧客向けの出荷が殆どで、あまり広範に展開する予定はないという話が聞こえてきていたが、結果的にこれを裏付けるような格好になった形だ。そもそも4/8 Socket製品を使う顧客は現状では極めて稀(殆どが2 Socket)であるが、ここに関しては今年末までに発表予定のIce Lake-SPと、来年登場のSapphire Rapidsでカバーするというのが現状のIntelの方針である。

さて、Cooper LakeのCascade Lakeに対してのアーキテクチャ的な違いはBfloat16の対応だけであって、これはAVX512に対しての拡張(AVX512_BF16)となる。ちなみに今のところ、このAVX512_BF16をサポートしているのはCopper Lakeのみであり、Ice Lake-SPがこれに対応するかどうかは不明である(少なくともIce Lakeは未対応)。Intel DL BoostことAVX512_VNNIとも切り離しての提供という扱いで、それもあって表現が"Intel DL Boost with bfloat16"となる訳だ(Photo02)。たださすがにこの結果としてAVX512は派生型が山ほど存在することになって、いい加減に統合したくなったのだろうか? Sapphire Rapidsでは新しいAMXなる拡張命令が投入されることが発表された。このAMXはAdvanced Matrix eXtensionsの略だそうで、今月中にはSpecificationが公開されるという話である。ちょっと怖いのが、次世代DL BoostがこのAMXになるというニュアンスの説明になっていることで、仮にAVX512全体の後継ではなく、AVX512_VNNIのみの後継だとしたら面倒な事になりそうな気もする。

-

Photo02: ものすごくラフな言い方をすれば、扱うデータ量が減るほど、より処理性能があがる(半面精度が落ちる)ということで、bfloat16は丁度Int 8とFP32の間に位置することになる。ただ世の中ではInt 1/2/4なども出てきているが、こちらは推論Onlyで学習には使わないので、とりあえずCooper Lakeでは対象としないのだろう。

ちなみにちょっと不思議なのが、Intel SST(Speed Select Technology)の実装である。SST自身は既に提供されている技術であるが、Cooper Lakeでこれに対応するのがXeon Goldの3製品だけ、というのはどういう理由なのか、現時点では不明である。

このCooper Lakeベースの第3世代Xeon Scalableプロセッサ、Xeon Platinum 8354Hを除き全て同日より出荷開始となっている。