米AMDは米国時間の8月7日、サンフランシスコにおいてAMD EPYC Horizon 2019というイベントを開催し、ここで第2世代EPYCプロセッサを発表した。

このイベントの模様はSocialでの中継可ということで、筆者もいくつかのスライドをMomentでまとめてある(Photo01)。

細かな話は稿を改めてご紹介するとして、まずはポイント(と、いくつか筆者が考え違いしていたこと)をまとめて簡単に説明すると

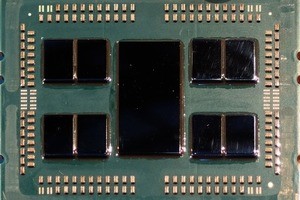

- 構成は最大8 Chiplet+I/O Chipletの構成で、最大64core/128Thread動作が1 Socketで実現可能。1 Socketの合計トランジスタ数は320億個にもおよぶ(Photo02)。

- CPU Chipletは既に発表済みのZen 2ダイを利用したもの。こちらのDeep Diveは既に入稿済みなので近日掲載されると思う。EPYC向けというか、Ryzen向けで無効化されていた機能(Security周りとか)でのハイライトは、初代EPYCに比べて、大幅に同時アクセス可能数が増えたことだろうか(Photo03)。

- Memoryは引き続き8chのまま。ただしDDR4-3200メモリのサポート(1DPCのみ)と、64Gbit DRAMの出現により256GB DIMMモジュールが入手可能となるので、1 Socketあたりの最大メモリ容量は4TBに達する。

- 7nmプロセスのZen 2ダイを利用することで動作周波数を引き上げつつ消費電力を下げ、かつコア数を倍増させたことで、性能は大幅に改善した。実際AMDは競合となるIntelのCascade LakeベースXeonと比較した上で、Xeonの2 Socket構成と同等の性能を1 Socketで実現できるとしている(Photo04)。

-

Photo03: 初代では同時に15種類のMemory Keyをサポートしていたが、第2世代ではこれが509に拡張された。もっともこれはZen 2コアというよりはI/O Chiplet側の機能であるが。

インナップは2 Socket向け(Photo05)が14製品、1 Socket向け(Photo06)が7製品。価格はスライドにはないが、プレスリリースによれば2 Socket向けが$475~$6950、1 Socket向けが$450~$6450(何れも1000個発注時の価格)となっており、やはりCascade LakeベースのXeonと比較して価格性能比が2倍~4倍優れている、としている。

また現在は第3世代の製品としてMilanの設計が完了しており第4世代のGenoaを設計中、という話であった(Photo07)。

もう少し具体的な性能比較、及びChiplet周りの話は、後日レポート予定である。