日立製作所は2月19日、実社会の複雑な問題を解くためのCMOSアニーリングマシンを名刺サイズへ高集積化するとともに高速化を図り、エネルギー効率を大幅に高めることに成功したと発表した。

-

日立が開発したCMOSアニーリングマシン

, CMOSアニーリングマシンとは、磁性体の性質を説明するために考案されたイジングモデルを用いて組合せ最適化問題を解くために日立が開発している新型コンピュータ。

今回開発されたCMOSアニーリングマシンのサイズは91×55mm2で、約6万パラメータの組合せ最適化問題の計算を従来型コンピュータの約2万倍高速で行うことができ、エネルギー効率を約17万倍に向上した。

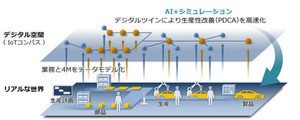

同マシンは、組み合わせ最適化問題の計算をスマートフォン、カメラ、センサなどのIoT機器でリアルタイムに行うエッジ処理への適用可能性を見据えたものだという。

今回開発された技術は高集積化を実現する回路技術と高速計算を可能とするチップ間接続技術。

高集積化を実現する回路技術としては、今回、パラメータの値を保持するメモリセルへのデータアクセスを高速化することで、演算順序に従って1つの演算回路を4つのパラメータグループの間で切り替えながら共有できる技術を開発。これにより演算回路の数を削減でき、メモリセルの集積度を従来の1.5倍*11に高め、1チップで30,976パラメータの高集積化に成功したという。

高速計算を可能とするチップ間接続技術としては、半導体チップの端部に、別チップのパラメータの値をコピーするための補助領域を設け、パラメータグループを計算する間に、次のパラメータグループのコピーを完了できるチップ間接続技術を開発。

さらに、開発した技術を搭載したチップを2枚接続し、名刺サイズ(91 × 55 mm2)で61,952パラメータの最適化問題の計算が可能なCMOSアニーリングマシンを開発した。