マイクロアーキテクチャをSkylake世代に

Xeon Processor Scalable Familyでは、マイクロアーキテクチャをSkylake世代に刷新している。これはクライアント向けのものとほぼ同じだが、データセンター向けにのスペック強化として、AVX-512命令をサポートするための演算器を追加したほか、256KBのMLC(L2キャッシュ)に対してさらに768KBを増設することで計1MBとした。

AVX-512のサポートに合わせてクロックの振る舞いも変更している。AVX-512は、第2世代Xeon Phi(開発コード名:Knights Landing)からサポートしているが、Hisa Ando氏のレポートによると、AVX-512を頻繁に使うような場合では動作クロックを下げる挙動になっているという。

Xeon Processor Scalable Familyでも同じように、AVXを使わないケース(SSEやAVX2を軽く使う場合)、AVX2を頻繁に使うケース(AVX-512を軽く使う場合)、AVX-512を頻繁に使うケースで、それぞれ動作クロックを調節する。なお、動作クロックの調整は各コアで独立して行われる。IntelではAVX-512によって、性能と効率の両方を大幅に向上できるとアピールする。

コア間のインターコネクトをリングからメッシュに変更

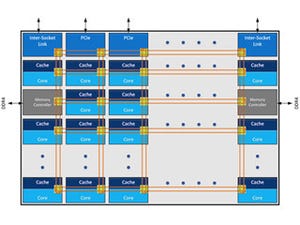

さて、既報の通りXeon Processor Scalable Familyでは、CPUコア間やキャッシュメモリのインターコネクトを従来のリングバスによる接続から、メッシュアーキテクチャに変更した。

| ・Intel、新Xeonファミリーでメッシュアーキテクチャを採用へ |

|---|

前世代までのXeonを含めてIntel CPUで採用しているリングバスによる接続では、CPUコアが増えるごとにコア同士やI/Oユニットとの距離が生じていた。特に10コアを超えるような場合では、2つのリング間をバッファースイッチで接続するため、リングをまたいでLLC(L3キャッシュ)にアクセスするときなどで、レイテンシが増えてしまっていた。

これに対し、Xeon Processor Scalable Familyでは、CPUコアやキャッシュ、メモリコントローラを網目のように配置するメッシュ構造とすることで、CPUコア間やメモリコントローラなどとの間において短い経路でデータ転送が可能になる。これにより、バンド幅の増加やレイテンシの低減、電力消費の削減が実現できるほか、コアの増加したときの、電力消費やレイテンシの増大も抑えられるという。

ただし、大原雄介氏による「Core X」シリーズの検証結果を見る限りでは、コア数が少ない場合、リングバスでの接続よりもメッシュではレイテンシが増える傾向にあるようだ。

| ・Core i9-7900XとCore i7-7820Xを試す - いち早く登場する10コアと8コアCPUのパフォーマンスを徹底検証 |

|---|

各コアには、キャッシュエージェントとホームエージェントを統合したCaching and Home Agent(CHA)、スヌープフィルタ、L3キャッシュスライスが付く。CHAはアクセスされるL3キャッシュスライスのアドレスを、メモリコントローラやIOサブシステムにマッピングして、効率的な伝送経路を提供する。CHAを各コアに分散することで、メッシュ内のトラフィックス削減や、早い段階でスヌープし、レイテンシを削減できるとする。

なお、Xeon Processor Scalable Familyのダイバリエーションは、前世代と同じHCC(High Core Count)/MCC(Middle Core Count)/LCC(Low Core Count)の3種類で、HCCが28コア、MCCが18コア、LCCが10コアとなる。

キャッシュ階層も大きく変化 - L3がノンインクルーシブに

Skylake-SPコアでは、コア当たりのL2キャッシュが256KBから1MBへ増えたと紹介したが、L3キャッシュは逆に従来の2.5MBから1.375MBと削減された。さらにL3キャッシュをインクルーシブキャッシュからノンインクルーシブキャッシュへと変更になった。

L2キャッシュの容量を増やすことで、ヒット率が向上し、メッシュのモジュールやL3キャッシュへのトラフィックを抑えることができる。加えて、L3キャッシュをノンインクルーシブにした場合、L2キャッシュとL3キャッシュで重複する内容がないため、キャッシュ全体を効率的に利用できるという。

メモリコントローラも強化。ソケット当たりのコントローラ数は前世代と同じ2基だが、1基当たり3チャンネル、合計で6チャンネルをサポートし、最大1.5TBまでのメモリが搭載可能だ。また、最大メモリスピードもDDR4-2400からDDR4-2666に強化。ソケット当たりのメモリバンド幅が60%向上している。

新たなCPU間インターコネクトやストレージ管理技術も

CPU間のインターコネクトは従来のQPIからUPI(Ultra Path Interconnect)に置き換わった。基本的にはQPIを強化したもので、データレートが9.6GT/sから10.4GT/sに向上したほか、データ効率の改善やアイドル時の電力消費削減を実現している。

I/OではPCI Express x16コントローラを、HCCで4基、MCCとLCCで3基搭載している。HCCのPCI Express x16コントローラのうち1基はOmni-Pathとの接続用に使われるので、実際のPCIeレーン数としては48レーンとなる。Omni-Pathは今回からチップ側にインタフェースを統合可能になった(オプションでの対応)。CPUに直結されたコネクタと専用ケーブルでモジュールを接続する形を採る。

また、高速SSDを管理するための新技術「Intel VMD(Volume Management Device)」も追加されている。従来はSATAなどで接続したストレージをソフトウェアで管理していたが、PCIe SSDのような広帯域で接続するストレージの場合、ソフトウェアでは遅延が発生するため、ハードウェアで管理をサポートするというものだ。

Core Xシリーズでも対応する仮想RAID技術「Intel VROC(Virtual RAID on CPU)」は、Intel VMDによるソリューションで、PCIe SSDでRAIDアレイを構築してもブートドライブとして利用できる。

チップセットも大幅強化

対応チップセットであるIntel C620(開発コード名:Lewisburg)も、前世代のIntel C610(開発コード名:Wellsburg)から、機能やインタフェースを大幅に強化している。

Intel C620では、これまでディスクリートの形で提供してきた、データの暗号化や圧縮用のハードウェアアクセラレータである「Intel QuickAssist Technology」をチップセット側に統合した。IntelによるとAES256 + HMAC SHA256による暗号化で従来比3倍、RSA 2048 Decryptの公開鍵暗号で2.5倍、データ圧縮で4倍の性能向上を実現したという。

また、ネットワーク機能として、前世代ではGigabit Ethernetのサポートに留まっていたところ、Intel C620では4基までの10Gbit/Gigabit Ethernetに対応するネットワークコントローラ「Intel Ethernet Connection X722」を統合する点も特徴の1つだ。

Intel Ethernet Connection X722は、40Gbit/10Gbitに対応したネットワークアダプタ「XL710」のIPをベースとしたもので、PHYを備えた10Gbit対応ないしは、Gigabit Ethernet対応の拡張カードを用いることで最大4基の10Gbit/Gigabit Ethernetをサポートする。