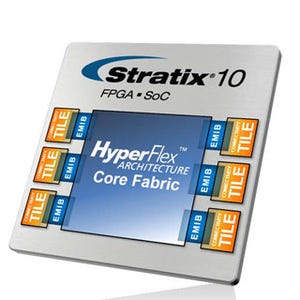

Alteraは11月9日(米国時間)、SK HynixのHBM2スタック・メモリとハイエンドFPGA/SoC「Stratix 10」を統合した「ヘテロジニアス SiPデバイス(Stratix 10 DRAM SiP)」を発表した。

同製品は、高性能システムの厳しいメモリ帯域幅要件に対応するために、IntelのEMIB(Embedded Multi-Die Interconnect Bridge)テクノロジーを用いて設計されたデバイスで、現在市販されているディスクリートDRAMソリューションの10倍以上のメモリ帯域幅を実現する。

Alteraでは、ヘテロジニアスSiP戦略として、モノリシックFPGAとメモリ、プロセッサ、アナログ、オプティカル、各種ハード・プロトコルなどのコンポーネントを1パッケージに統合することを掲げており、通信、高性能コンピューティング、放送、および防衛分野といったハイエンド・アプリケーションにおける厳しい性能とメモリ帯域幅要件に対処していくとしている。

なお、Stratix 10を使用したデザイン開発は、Fast Forward Compile性能評価ツールを使用することで即座に利用可能だという。また、Stratix 10 FPGA & SoCは2016 年に、Stratix 10 DRAM SiP製品は2017年にそれぞれ出荷を開始する予定としている。