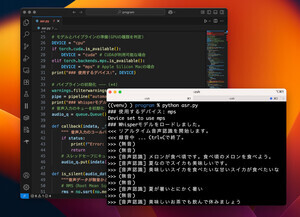

ON Semiconductorは1月8日、従来のモノリシックの非スタック型設計と比較してダイサイズ、ピクセル性能、および消費電力を改善し、全機能を搭載したスタック型CMOSイメージセンサの特性評価および実証に成功したと発表した。

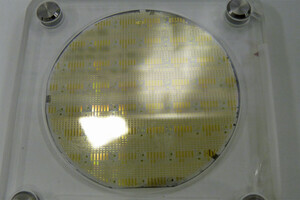

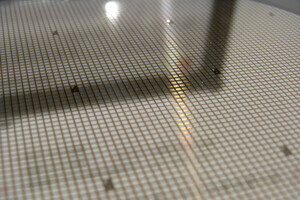

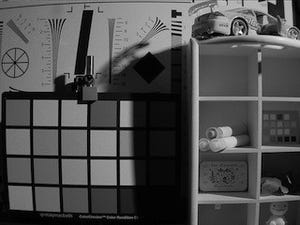

モノリシック基板プロセスによる従来のセンサ設計では、ピクセル配列と下層の回路をサポートするために別々のダイエリアが必要である。これに対し、3Dスタッキング技術では、ピクセル配列と下層の回路は、別々の基板で製造され、シリコン貫通電極(Through Silicon Vias:TSV)で2つを接続してスタックされる。これにより、ピクセル配列を下層の回路に重ね合わせることができ、より効率的なダイレイアウトが可能になる他、画像性能、コスト、消費電力、およびダイサイズに合わせてセンサ各部の最適化が図れる。さらに、ピクセル配列の最適化により、センサはノイズレベルの削減とピクセル応答の改善を通してピクセル性能を向上させることができる。また、下層の回路は、消費電力を減らすために、より積極的な設計ルールを利用できる。そして、全体的な面積が縮小することで、光学式手ぶれ補正(OIS)と追加のデータストレージが同じモジュール面積に組み込まれた最先端のカメラモジュールをサポートできるとしている。

なお、同技術は1.1μmピクセルのテスト用チップの実装に成功して特性評価を完了させており、今年後半には製品に組み込まれる予定。