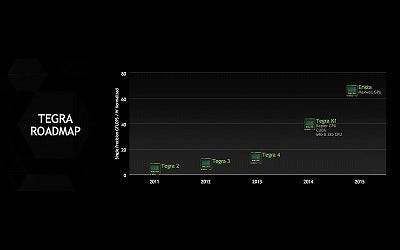

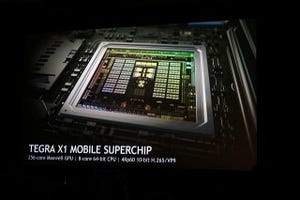

NVIDIAは、米国時間の1月4日、ネバダ州ラスベガスのフォーシーズンズホテルにおいて記者発表会を開催し、次期モバイルSoC(System on Chip)となる「Tegra X1」を発表した。同SoCは、これまで開発コードネーム"Erista"(エリスタ)と呼ばれてきたものであり、その製造プロセスにはTSMCの20nmプロセスが採用されることも明らかにされた。概要はお届け済みだが、本稿ではTegra X1の詳細をレポートしたい。

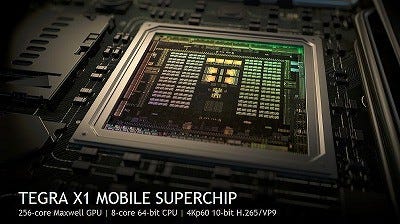

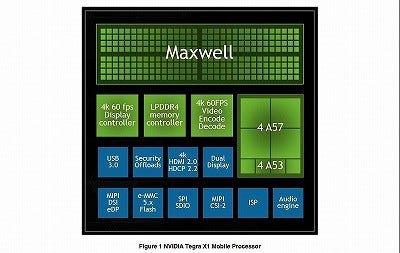

同製品は、GPUアーキテクチャにGeForce GTX 980で採用されている第2世代のMaxwellアーキテクチャを採用し、256 CUDAコアを統合するとともに、CPUコアには64bit ARMアーキテクチャであるARMv8に対応したCortex-A57とCortex-A53を4基ずつ、合計8コアをbig.LITTLE構成で搭載する。

この両ARMコアは、ARMの64bitアーキテクチャであるARMv9に対応したコアで、Cortex-A57がハイパフォーマンス、同A53が省電力処理を担当することで、限られたTDP(Therm Design Power)でもパフォーマンスと省電力性能を両立させる。Tegra X1に採用された、Cortex-A57コアは、48KBのL1命令キャッシュと、32KBのL1データキャッシュを各コアに統合し、4つのコアで2MBのL2キャッシュを共有する構成を採っている。一方のCortex-A53は、各コアとも32KBのL1命令キャッシュと32KBのL1データキャッシュを統合し、4つのコアで512KBのL2キャッシュを備える。なお、big.LITTLE構成では、熱設計に余裕があれば、8つのコアを同時に動作させることも可能だが、Tegra X1が8コア動作に対応しているか否かは、現時点では分からない。

|

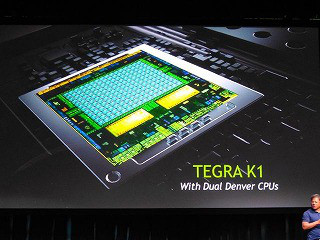

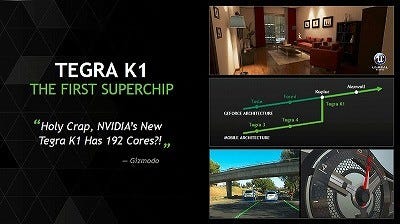

NVIDIAは、現行のTegra K1で、最新グラフィックスアーキテクチャとの統合するとともに、CUDAへの対応を果たし、GPUコンピューティング機能も備えた"スーパーチップ"へと進化したと位置づけていた |

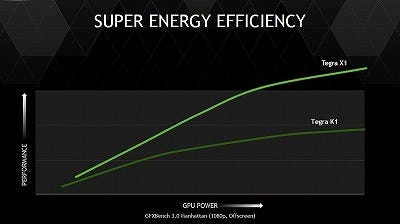

NVIDIAの共同創始者兼CEOのジェンスン・ファン氏は、同SoCのグラフィックス性能についても、いくつかのベンチマーク指標を公開し、Tegra X1は、AppleのA8xプロセッサやTegra K1に比べて、1.5倍から2倍のパフォーマンスを発揮すると説明。その、電力効率は、Tegra K1を大きく上回り、Unreal Engine 4の"Elemental"デモを実行するのに、「2年半前のわれわれのGPUでは300Wが必要だった。最新ゲームコンソールのXbox Oneで100W以上を要するのに対し、Tegra X1では約10Wで同等のグラフィックス表現やパフォーマンスを実現するとして、実際にTegra X1によるデモを披露した。

| 動画 |

|---|

| Tegra X1によるElementalのデモ映像 |

さらに、Tegra X1ではVPE(Video Processing Engine)と呼ぶビデオ機能も大幅に強化され、H.265対応やGoogleの最新動画圧縮技術であるVP9をサポートし、10bitの4K(3,840×2,160ピクセル)表示を60Hzのリフレッシュレートで出力できるようになるとともに、外部ディスプレイインタフェースとして、HDMI 2.0およびHDCP 2.2対応が追加された。

とはいえ、Tegra X1はモバイルSoCとして設計されており、チップサイズや消費電力の制約が大きい。そこで、NVIDIAでは、第2世代Maxwellで採用したカラー圧縮技術などのメモリ圧縮と、LPDDR4メモリへの対応を果たすことで、64bitメモリインターフェースながら、25.6GB/secのメモリ帯域を確保。さらに、4Kピクセル出力を効率的に行なえるよう、ROP(Raster OPeration)ユニットを、従来の4倍となる16基搭載しているのも特徴だ。

なお、Tegra X1の基本仕様は、下記の表のとおりだ。

| ■Tegra X1とTerga K1の基本仕様 | |||

| Tegra X1 | Tegra K1 | Tegra K1(64bit) | |

|---|---|---|---|

| 製造プロセス | TSMC 20nm | TSMC 28nm | TSMC 28nm |

| CPUコア | ARM Cortex A57×4 ARM Cortex A51×4 |

ARM Cortex A15×4+1 | NVIDIA Denver×2 |

| GPUアーキテクチャ | Maxwell | Kepler | Kepler |

| CUDAコア | 256 | 128 | 128 |

| SM | 2 | 1 | 1 |

| ジオメトリユニット | 2 | 1 | 1 |

| テクスチャユニット | 16 | 8 | 8 |

| ROP | 16 | 4 | 4 |

| メモリインタフェース | 64bit LPDDR4/LPDDR3 | 64bit LPDDR3 | 64bit LPDDR3 |

| 最大メモリクロック | 1.6GHz (LPDDR4) | 930MHz | 930MHz |

| 最大メモリ帯域 | 25.6GB/sec (LPDDR4) | 14.9GB/sec | 14.9GB/sec |

| ピーク演算性能(FP32) | 512GFLOPS | 365GFLOPS | 365GFLOPS |

| ピーク演算性能(FP16) | 1024GFLOPS | 365GFLOPS | 365GFLOPS |

| H.264 | 4K/60Hz | 4K/30Hz | 4K/30Hz |

| H.265 | 4K/60Hz(10bit) (エンコードは 4K/30Hz) |

- | - |

| VP8 | 4K/60Hz | 4K/30Hz | 4K/30Hz |

| VP9 | 4K/60Hz | - | - |

| HDMI | 2.0 | 1.4b | 1.4b |

| HDCP | 2.2 | 1.4 | 1.4 |

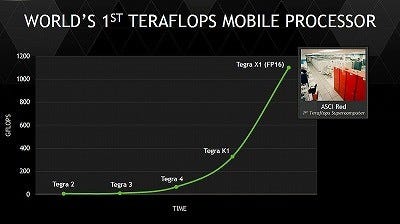

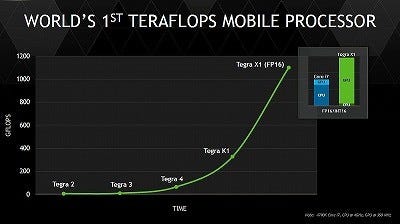

また、ファン氏はTegra X1は、モバイルSoCとして初めて浮動小数点演算性能が1テラFLOPSを超えたスーパーチップだと説明。1997年にはじめて1TFLOPSの演算性能を実現したスーパーコンピュータ「ASCI Red」では、「4000基以上のIntel Pentium Proプロセッサを搭載し、150平方メートルの設置面積と500kWの消費電力を要した」(ファン氏)と、その電力効率の高さをアピールした。

|

|

Tegra X1では、FP16であれば1テラFLOPSを超える演算性能を実現。この"数値"は、1997年に初めて1テラFLOPSを超える演算性能を実現したスーパーコンピュータ「ASCI Red」と同じものであり、Intel Core i7よりも優れた性能だとアピール |

ただし、この1テラFLOPSという値は、通常の単精度浮動小数点演算ではなく、FP16、すなわち"半精度"の演算性能。Tegra X1に搭載されたCUDAコアでは、二つのFP16命令をパックして実行できるようにすることで、単精度浮動小数点演算(FP32)の倍の演算性能を引き出すことを可能にしている。むろん、ASCI Redが実現した倍精度(FP64)による1テラFLOPSと同等に扱うべき値でないことは、ファン氏も認めるところだ。

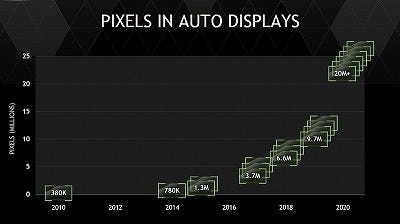

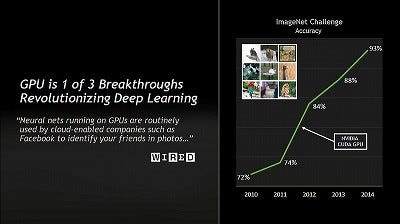

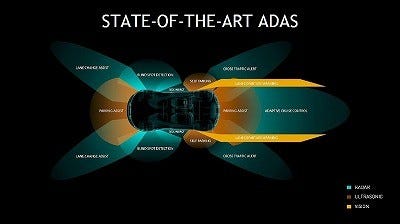

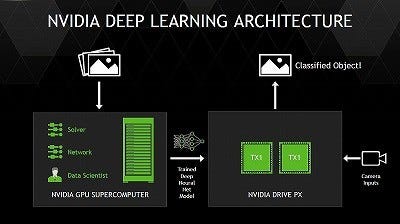

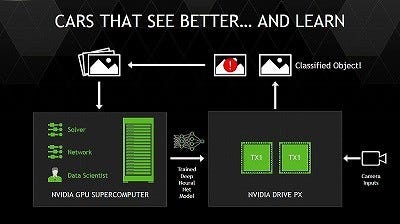

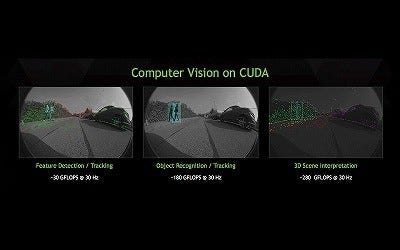

また、同氏は「1テラFLOPSという演算性能は、スマートフォンには不要だ」とも断言。同氏がTegra X1の市場として注目するのは、今後、巨大コンピューティングマーケットとして成長が期待されるオートモーティブ市場だ。同社は、この1テラFLOPSという演算性能を、よりインテリジェントな次世代先進運転支援システム(ADAS: Advanced Driver Assistance Systems)や自動運転などを実現するために利用することで、オートモーティブ市場における同社の優位性を確立させたい考えだ。

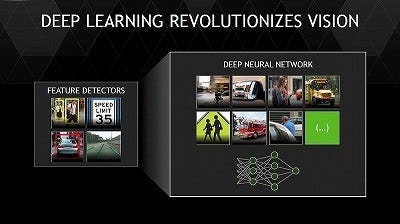

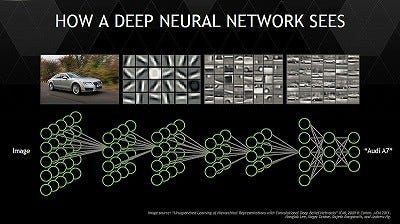

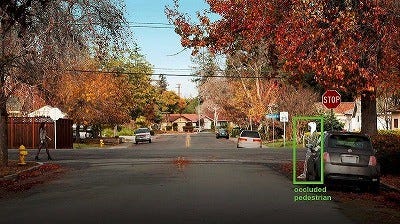

ファン氏は、「Tegra X1では、コンピュータ自身が学習して情報処理を行なうニューラル・ネットワーク(Neural network: 神経回路網、脳神経をモデルにした学習能力をもった情報処理システム)によって、より洗練されたADASや自動運転が可能になる」として、CUDAを使った歩行者や車両、交通標識や信号などの認識システムのビデオデモを披露。

同システムでは、自動車に搭載された複数のカメラで捉えたオブジェクトを、より少ないピクセル要素の組み合わせで特定し、安全な運転を実現しようというもので、ニューラル・ネットワークを利用したディープ・ラーニング(深層学習)によって、走行中の車両を単に認識するだけでなく、車両の種類を特定し、緊急車両やスクールバスといった、運転上注意が必要な車両が接近中であることをドライバーに伝えたり、スマートフォンを歩きながら使っている歩行者など、注意が必要な歩行者の存在を警告するといった、より動的な運転支援システムを実現できるようになると言う。

|

|

NVIDIAは、先進運転支援システムへのGPUの活用技術の開発にTegara K1世代から取り組んでおり、Tegra X1ではディープ・ラーニングへの対応により、より洗練されたシステム開発を可能にする |

| 動画 |

|---|

| 同社が開発している運転支援システムによる、交通標識認識の技術デモ映像 |

同社でGPUを利用した運転支援システムなどの開発を担当するシニアエンジニアのマイク・ヒューストン氏(AMDのGCNアーキテクチャの開発者の一人としても知られる)は、この運転支援システムでは、レーダーなどは利用せず、複数のカメラの映像をリアルタイムで画像処理しているため、比較的低コストで先進運転支援システムを実現できる。

同社が、レーダーではなくカメラにこだわるのは「レーダーのほうが、前方の車両との距離などのデータは取得しやすいが、45°角で照射した場合、側方に駐車車両があったり、追い越しをかけられると、反射によってレーダーが正しく受信できないことがあるため、カメラベースのシステムのほうが汎用性が高い」と指摘。また、夜間走行時のオブジェクト認識を容易にするため、多くの自動車メーカーはモノクロカメラを利用しているため、半精度演算処理で高速化が図れるメリットは大きいと説明する。

|

|

車にスーパーコンピュータが搭載できるとすれば、その演算性能の助けを借りて、高解像度カメラだけで、先進運転支援システムが構築できると、Tegra X1の優位性をアピール。将来的には同システムを使った自動運転も実現可能だと見る |

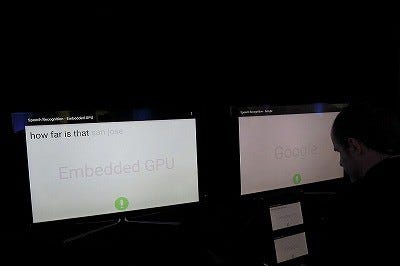

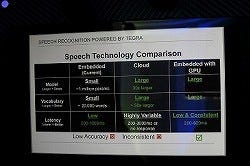

さらに同社は、インターネット環境がない状況でも、高精度の音声認識を実現すべく、GPUを使った音声認識のデモも披露した。同デモは、Tegra K1を採用したSHIELD Tabletで行なわれたが、一般的に常用される語彙数の範囲であれば、SDカードなどにデータを保存しておき、ローカルで音声認識を行なっても、クラウドベースのGoogle音声認識よりも優れたパフォーマンスと省電力性を実現できるとアピール。インターネット接続がない状況でも、ドライバーがストレスを感じることなく安全に車載コンピュータを操作できるようにできると言う。

|

GPUを使った音声認識と、クラウドベースのGoogle音声認識のデモ。GPUを使った音声認識のほうがレスポンスで上回り、精度でも大型コンピュータで処理を行なうGoogle音声認識と差がない結果となった |

|

|

現在の音声認識システムでは、遅延時間や精度の低さが課題となっている |

音声認識技術の比較。CPUベースや、クラウドベースの音声認識よりも、GPUベースのほうが、精度やレスポンスのバランスで優位だとアピール。なお、このデモではTegra K1ベースのSHIELD Tabletが利用された |

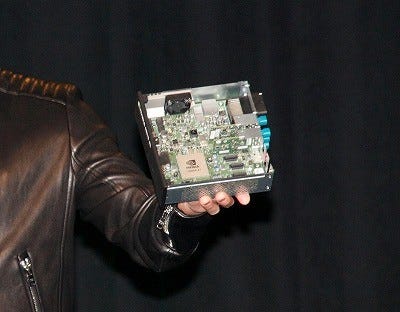

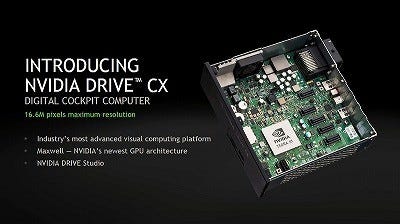

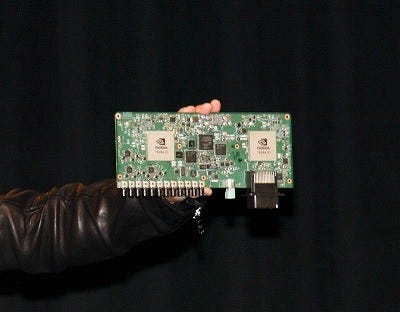

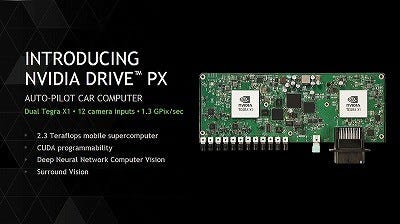

NVIDIAは、このTegra X1の車載向けシステムとして、コンソール表示やナビゲーション、車内エンターテイメントを提供するプラットフォームの「DRIVE CX」と、Tegra X1を2基搭載し、自動車の自動運転や、ディープ・ラーニングを実現するプラットフォーム「DRIVE PX」を発表した。

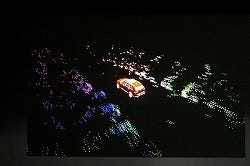

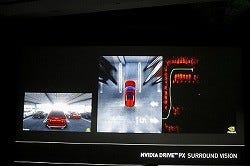

このうち、DRIVE PXでは、最大12基のカメラ入力チャネルをサポートし、2.3テラFLOPS、1.3ギガピクセル/secの処理性能を実現。同システムを利用した先進運転支援システムでは、30fpsで最大150種類のオブジェクトを認識することができると言う。NVIDIAでは、この性能を活かして、前後左右4つのカメラの映像から、障害物などのオブジェクトを認識し、各カメラの映像を2Dに変換後、4つのカメラのデータから、車の周辺環境を3Dマッピングしなおす"Surround Vision"を使い、自動車が無人で駐車スペースを探し、駐車する"Auto-Valet"のテクノロジデモも披露した。

このデモは、実際の駐車場で無人運転の試験車両を走らせるのではなく、5基のGeForce GTX 980を搭載したシステムでリアリスティックな仮想空間を構築し、その中で自動駐車のシミュレーションを行なえるようにすることで、自動運転のアルゴリズムやソフトウェアなどを開発できるようにするというもの。これにより、自動車メーカーは、自動運転システムのハードウェア開発と並行して、ソフトウェアの開発をスタートさせることができるだけでなく、Tegra X1がサポートするディープ・ラーニングを活用して、独自のアルゴリズム開発を進めることにも役立つとアピールする。

ファン氏は、その成果の一つとして、2011年から協業をスタートさせた独Audi社の事例を紹介。Audi社で、自動運転車両の開発などを指揮するリッキー・フディ上級副社長(Executive Vice President of Electronics Development)は、NVIDIAのSoCを利用した自動運転テスト車両で、最高時速240km/hでのサーキット走行を実現したり、CES開幕にあわせてシリコンバレーからラスベガスへの長距離無人ドライブテストを行なったりと、自動運転がそう遠くない未来に実現すると宣言。さらに同氏は、NVIDIAとの協業により、これまで5年ほどかかっていたコンピューティングデバイスの実装が、約1年ほどに短縮されつつあるとして、年内にはNVIDIAが昨年発表したTegra K1を、来年にはTegra X1を採用したモデルを市場投入できるという見通しを示した。

NVIDIAとしては、スーパーコンピュータ市場などで圧倒的な支持を得ているCUDAの成功事例をオートモーティブ分野にも適用することで、競合他社の追撃が始まる前に、一定の市場シェアを固めてしまおうという狙いも見え隠れする。その意味では、Tegra X1でMaxwellアーキテクチャをさらに拡張し、FP16のサポートを追加することで1テラFLOPSの演算性能をいちはやく実現するとともに、複数のカメラを利用した走行環境認識やディープラーニングの開発環境を、パートナーに提供できるようにしたことは、未来の自動車市場における基盤を整える大きな一歩となりそうだ。